DPLL PRESENTATION

-

Upload

narendra-naidu-lingutla -

Category

Documents

-

view

312 -

download

0

Transcript of DPLL PRESENTATION

DIGITAL PHASE LOCKED LOOP

E E-524 DIGITAL VLSI LABORATORY

SAM VIVIN RAJ KRISHAN HIMAKAR REDDY GADDAMNARENDRA NAIDU LINGUTLA

December 12 , 2014

OUTLINE

Introduction Specifications Design Schematics of Major Blocks Test Benches of Major Blocks Schematic and Test Bench of DPLL Challenges

INTRODUCTION

Digital Phase Locked Loop: Multiply Clock Frequency Clock Synchronization Less stable than DLL(2nd order)

Applications: Telecommunications Clock synchronization and multiplication in Micro processors Clock generation

SPECIFICATIONS

Name Value

Process SS, TT, FF

Supply 1.6V -1.98V

Temperature -40 C – 127 C

Input frequency 100 MHz

Output Frequency 1 GHz, 900MHz , 800MHz

Load 10 pF

SPECIFICATIONS

BLOCK DIAGRAM OF PHASE LOCKED LOOP

PHASE DETECTOR

LOOP FILTER

DIVIDE BY 10

Fout

Feedback Signal(Fout/N)

Finput

PUSH

PULL

VCO

UP

Down

Ipd

Vcntrl Vout

CLOCKBUFFER

DIVIDE BY 8

DIVIDE BY 94X1 MUX

TEAM CONTRIBUTION

Schematics & Simulation :

Phase Detector , Push-Pull Charge Pump – Himakar Gaddam Loop filter ,Voltage Control Oscillator , Clock Buffer - Sam Vivin

Raj Frequency Divider , Multiplexer - Narendra

Naidu

Overall Simulation and test bench – Sam , Himakar , Narendra

DPLL – DESIGN CALCULATIONS

fin = 100MHz; fout = 1GHz; Supply Voltage = 1.62V; Process - SS Loop Bandwidth – ωn

ωn = ωin/50 = 2πfin/50 = 12.57Mrad/sec

Damping Factor – ζ C = 10pF, C2 = C/10 = 1pF ζ = 1.25 (Slightly over damped, almost critically damped) ζ = 0.5ωnRC R = ζ/(0.5ωnC) R = 19.9KΩ (in loop filter)

Contd..

For 5 stage VCO;

Vin = Vctrl =(1.62 + 0.47) / 2 = 1.045V

N = 5, VDD = 1.62V, Vth = 0.47V ID = 52.97 μA

R = 10.86kΩ;

Kvco = 475Mhz/V ( from the simulation)

6C = 6.54fF;

Contd..

where N = 10 =

Icp = 33.26μA Rlarge =34.57Ω

MAJOR BLOCKS SCHEMATIC, TESTBENCH AND SIMULATIONS

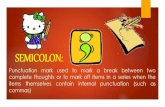

PHASE DETECTOR

Desired Parameters:

fin = 100MHz;

fout = 1GHz; fout/10 = 100MHz

fout = 900MHz; fout/9 = 100MHz

fout = 800MHz; fout/8 = 100MHz

During testing

• fclkA = 100MHz

• fclkb = 95MHz

PHASE DETECTORSCHEMATIC:

PHASE DETECTORTEST BENCH:

load

PHASE DETECTORSIMULATION RESULTS:

Fin=100MHz

Fout =95MHz

UP

DOWN

Push – Pull Charge pump

Desired parameters :

For 5 stage VCO;Kvco = 475MHz/V

Push pull charge pump

Icp = 33.26μA

Rlarge = 34.57kΩ

PUSH-PULL CHARGE PUMPSCHEMATIC:

Rlarge = 34.57K ohms

Rlarge

UP BAR

DOWN

PUSH-PULL CHARGE PUMPTEST BENCH:

UPBAR

DOWN

Load

UP BAR

DOWN

Load

PUSH-PULL CHARGE PUMPSIMULATION RESULTS:

Ipd

UPBAR

DOWN

Icp

DOWN

UP

Vcntl

Vcntl = 1.045V

Loop Filter

Desired Parameters :

Capacitance(C) = 10pF, C2 = 1pF Loop Bandwidth – ωn

ωn = 12.57Mrad/sec

Damping Factor – ζ ζ = 1.25 (Slightly over damped, almost critically damped)

R = 19.9kΩ

LOOP FILTER SCHEMATIC

Voltage Controlled Oscillator(VCO)

Desired Parameters :

For 5 stage VCO;

Vin = Vctrl =(1.62 + 0.47) / 2 = 1.045V

N = 5, VDD = 1.62V, Vth = 0.47V ID = 52.97 μA

R = 10.86kΩ;

Kvco = 475Mhz/V

6C = 6.54fF;

VOLTAGE-CONTROLLED OSCILLATORSCHEMATIC:

R = 6.39K ohmsVcntrl = 1.045 VVDD = 1.62V ; VSS = 0

VOLTAGE CONTROL OSCILLATORTEST BENCH:

VOLTAGE CONTROL OSCILLATORSIMULATION RESULTS: Freq = 1GHz

VOLTAGE CONTROL OSCILLATORSIMULATION RESULTS:

Kvco = 475Mhz/V

VOLTAGE CONTROL OSCILLATORSIMULATION RESULTS:

Freq = 900MHzR = 8.62K ohmsVcntrl = 1.045 VVDD = 1.62V ; VSS = 0

VOLTAGE CONTROL OSCILLATORSIMULATION RESULTS:

Kvco = 596Mhz/V

VOLTAGE CONTROL OSCILLATORSIMULATION RESULTS:

R = 11.17K ohmsVcntrl = 1.045 VVDD = 1.62V ; VSS = 0

Freq = 800MHz

Kvco = 663Mhz/V

VOLTAGE CONTROL OSCILLATORSIMULATION RESULTS:

CLOCK BUFFER Design:

H=Cout / Cin = 10pF/3.27fF = 3058.1 G = 1, B = 1 F = GBH = 1*1*3058.1 = 3058.1. Taking ρ= 4;

N = Log43058 = 5.789 N = 6 stages

= 3.81

CLOCK BUFFER TEST BENCHSCHEMATIC:

Clock Buffer Test BenchTest bench:

CLOCK BUFFER TEST BENCHSIMULATION RESULTS:

IN

Frequency Divider

Design :

Divide by 10,9,8

Components used:

XOR Gate , Nor2x1 , Nand2x1

Flip – Flops

AND Gate

DIVIDE BY 10 CIRCUITSCHEMATIC:

DIVIDE BY 10 CIRCUITTEST BENCH:

DIVIDE BY 10 CIRCUITSIMULATION RESULT:

DIVIDE BY 9 CIRCUITSCHEMATIC:

DIVIDE BY 9 CIRCUITTEST BENCH:

DIVIDE BY 9 CIRCUITSIMULATION RESULT:

DIVIDE BY 8 CIRCUITSCHEMATIC:

DIVIDE BY 8 CIRCUITTEST BENCH:

DIVIDE BY 8 CIRCUITSIMULATION RESULT:

4X1 MULTIPLEXER :

SCHEMATIC :

4X1 MULTIPLEXER :

TESTBENCH :

4X1 MULTIPLEXER :

WAVEFORM 1 :S0 = 1; S1 = 0 Y = D1 = In2

4X1 MULTIPLEXER :

WAVEFORM 2 :

S0 = 0; S1 = 1 Y = D2 = In3

4X1 MULTIPLEXER :

WAVEFORM 3 :S0 = 0; S1 = 0 Y = D0 = In1

SIMULATION OF ENTIRE PROJECT

DIGITAL PHASE LOCKED LOOPSCHEMATIC:

DIGITAL PHASE LOCKED LOOPTEST BENCH: Load =

10pF

DIGITAL PHASE LOCKED LOOP IN LOCKSIMULATIONS:

Freq = 1GHz Process corner –> SS; VDD –> 1.62; T = 125C

DIGITAL PHASE LOCKED LOOP IN LOCKSIMULATIONS:

Freq = 1GHz Process corner –> tt; VDD –> 1.8; T = 27C

DIGITAL PHASE LOCKED LOOP IN LOCKSIMULATIONS:

Freq = 900MHz Process corner – SS; VDD – 1.62; T = 125C

DIGITAL PHASE LOCKED LOOP IN LOCKSIMULATIONS:

Freq = 800Hz Process corner –> SS; VDD –> 1.62; T = 125C

Results

Fout = 1GHz Fout = 900Mhz

Fout = 800Mhz

Vcntl 1.045 1.045 1.045

Frequency divider N = 10 N = 9 N =8

Icp 33.26μA 23.85μA 19.1μA

Rlarge 34.57Kohm 48.21Kohm 60.20Kohm

R at VCO 6.39Kohm 8.62Kohm 11.17Kohm

At Process Corner – SS ; VDD – 1.62 ; T = 125’C

CHALLENGES

Adjusting R in VCO to get the required Frequency

Frequency dividers for divide by 9,10 circuits

Thank you