pract_xilinx92

-

Upload

controlcucuta -

Category

Documents

-

view

116 -

download

0

Transcript of pract_xilinx92

5/10/2018 pract_xilinx92 - slidepdf.com

http://slidepdf.com/reader/full/practxilinx92 1/94

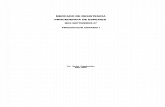

Departamento de Tecnología Electrónica

Diseño digital con esquemáticos y FPGA. v1.8

Felipe Machado Sánchez

Norberto Malpica González de Vega

Susana Borromeo López

5/10/2018 pract_xilinx92 - slidepdf.com

http://slidepdf.com/reader/full/practxilinx92 2/94

Departamento de Tecnología Electrónica

Diseño digital con esquemáticos y FPGA. v1.8 - - 04/06/2008 1

Índice

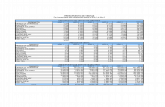

Índice .................................................................................................................................................................................. 1 1. Introducción..................................................................................................................................................................... 3 2. Encender un LED............................................................................................................................................................ 4

2.1. Diseño del circuito ............................................................................................................................................................................5

2.2. Síntesis e implementación del circuito............................................................................................................................................10 2.3. Programación de la FPGA..............................................................................................................................................................11 3. Puertas lógicas, interruptores y pulsadores .................................................................................................................. 15

3.1. Diseño del circuito ..........................................................................................................................................................................15 3.2. Simulación del circuito ....................................................................................................................................................................17 3.3. Síntesis e implementación del circuito............................................................................................................................................20

4. Decodificador de 2 a 4 .................................................................................................................................................. 21 4.1. Diseño del decodificador ................................................................................................................................................................21 4.2. Comprobación del diseño ...............................................................................................................................................................23 4.3. Implementación del diseño.............................................................................................................................................................24 4.4. Creación de un bloque....................................................................................................................................................................24

5. Decodificador de 3 a 8 .................................................................................................................................................. 27 5.1. Diseño del decodificador con bloques ............................................................................................................................................28

6. Decodificador de 4 a 16 ................................................................................................................................................ 30 6.1. Diseño del decodificador con bloques prediseñados .....................................................................................................................31 6.2. Comprobación del diseño ...............................................................................................................................................................33

7. Convertidor de hexadecimal a 7 segmentos ....................................................... .......................................................... 35 7.1. Diseño del convertidor de hexadecimal a 7 segmentos ................................................................................................................ 35 7.2. Implementación ..............................................................................................................................................................................39

8. Codificadores ....................................................... ........................................................................... .............................. 42 8.1. Codificador de 4 a 2 sin prioridad ................................................................................................................................................... 42 8.2. Codificador de 4 a 2 con prioridad, línea activa y habilitación........................................................................................................42 8.3. Codificador de 4 a 2 con conversión a 7 segmentos......................................................................................................................44

9. Extensión de la capacidad de un codificador .............................................................. .................................................. 46 9.1. Codificador de 8 a 3 a partir de codificadores de 4 a 2 .................................................................................................................. 46 9.2. Inclusión del convertidor a siete segmentos................................................................................................................................... 47 9.3. Codificador mayores....................................................................................................................................................................... 47

10. Comparadores ............................................................................................................................................................ 48 10.1. Comparador de un bit ...................................................................................................................................................................48 10.2. Comparador de dos bits ...............................................................................................................................................................48 10.2.1. Diseño del comparador ....................................................................................................................................................... 50

11. Comparadores en cascada ....................................................... ........................................................................ .......... 51 12. El multiplexor............................................................................................................................................................... 55

12.1. Especificaciones ...........................................................................................................................................................................55 12.2. Diagrama de bloques del circuito .................................................................................................................................................55 12.3. Diseño........................................................................................................................................................................................... 57

13. El sumador ........................................................... ......................................................................... .............................. 60 13.1. Especificaciones ...........................................................................................................................................................................60 13.2. Diseño........................................................................................................................................................................................... 60

14. Sumador/restador ....................................................................................................................................................... 63 14.1. Especificaciones ...........................................................................................................................................................................63 14.2. Diagrama de bloques....................................................................................................................................................................63

14.2.1. Bloque sumador/restador.................................................................................................................................................... 64 14.2.2. Bloque de visualización....................................................................................................................................................... 66 14.3. Diseño........................................................................................................................................................................................... 68

14.4. Comprobación del diseño.............................................................................................................................................................69 15. Unidad aritmético lógica.............................................................................................................................................. 71

15.1. Especificaciones ...........................................................................................................................................................................71 15.2. Diagrama de bloques....................................................................................................................................................................71 15.3. Diseño........................................................................................................................................................................................... 74

15.3.1. Multiplicador por 2 ...............................................................................................................................................................74 15.3.2. Circuito comparador, "mayor" ............................................................................................................................................. 75 15.3.3. Circuito operación lógica AND ............................................................................................................................................75 15.3.4. Multiplexor de 4 entradas datos con habilitación ................................................................................................................76 15.3.5. Codificador con prioridad de 4 entradas ............................................................................................................................. 77 15.3.6. Componente de mayor jerarquía.........................................................................................................................................78

15.4. Implementación y comprobación .................................................................................................................................................. 78 16. Elementos de memoria ............................................................................................................................................... 79

16.1. Especificaciones ...........................................................................................................................................................................79

16.2. Diseño........................................................................................................................................................................................... 79 16.3. Implementación ............................................................................................................................................................................79

17. Interruptor con pulsador .................................................... ...................................................................... .................... 81 17.1. Ideas .............................................................................................................................................................................................81

5/10/2018 pract_xilinx92 - slidepdf.com

http://slidepdf.com/reader/full/practxilinx92 3/94

Departamento de Tecnología Electrónica Índice

Diseño digital con esquemáticos y FPGA. v1.8 - 04/06/2008 2

17.1.1. Conectando el pulsador a la entrada del biestable T ..........................................................................................................81 17.1.2. Conectando el pulsador al reloj del biestable T .................................................................................................................. 81

17.2. Circuito detector de flanco ............................................................................................................................................................82 17.3. Solución al cronograma................................................................................................................................................................83

18. Parpadeo de un LED................................................................................................................................................... 84 18.1. Especificaciones ...........................................................................................................................................................................84 18.2. Diseño........................................................................................................................................................................................... 84

19. Reloj digital.................................................................................................................................................................. 87 19.1. Especificaciones ...........................................................................................................................................................................87 19.2. Contador de 10 segundos ............................................................................................................................................................87

19.2.1. Bloque segundero ...............................................................................................................................................................87 19.2.2. Bloque de mayor jerarquía .................................................................................................................................................. 89

19.3. Reloj digital con segundos y minutos ...........................................................................................................................................89 19.3.1. Implementación ...................................................................................................................................................................90 19.3.2. Solución...............................................................................................................................................................................91

5/10/2018 pract_xilinx92 - slidepdf.com

http://slidepdf.com/reader/full/practxilinx92 4/94

Departamento de Tecnología Electrónica 1. Introducción

Diseño digital con esquemáticos y FPGA. v1.8 - 04/06/2008 3

1. IntroducciónEl objetivo de esta prácticas guiadas es introducir al alumno en el diseño con esquemáticos mediante el usode herramientas CAD (computer aided design). Estas prácticas parten de un nivel elemental y se pretende quepuedan ser seguidas como complemento en un curso básico de electrónica digital. Estas prácticas se handesarrollado en el departamento de Tecnología Electrónica1 de la Universidad Rey Juan Carlos.

Estas prácticas consistirán en un grupo de ejercicios con los que aprenderemos a programar una FPGAutilizando la herramienta gratuita de diseño electrónico digital ISE-WebPACK de Xilinx2. En las prácticas deeste curso realizaremos diseños con esquemáticos: puertas lógicas, bloques combinacionales y secuenciales.Una vez que hayamos realizado el diseño en la herramienta, lo sintetizaremos y lo implementaremos en laFPGA. La síntesis es la tarea que transforma un diseño desde un nivel de descripción a otro nivel dedescripción más bajo. En nuestro caso, el diseño lo tendremos en esquemáticos y la herramienta lotransformará en una descripción que indica las conexiones internas y configuración de la FPGA para quefuncione de la misma manera a como funcionaría nuestro diseño original en esquemáticos. Por suerte, lasíntesis la realiza la herramienta automáticamente, durante la síntesis nosotros nos ocuparemos desupervisar el proceso, analizando los errores y advertencias (warnings) que aparezcan.

Antes de implementar el diseño en la FPGA es recomendable simular el diseño para comprobar quefunciona correctamente. Es más fácil detectar errores de diseño mediante simulación, que en la placa.

Imagina que has implementado el diseño en la FPGA y que ésta no hace nada. Para descubrir el fallotendrías que usar un polímetro o un osciloscopio y comprobar los niveles de tensión de los pines. Ademáscon el inconveniente de que sólo tienes accesibles los puertos de entrada y salida, y no las señales internasdel diseño. Mediante la simulación puedes comprobar todas las señales (internas y externas) y directamentede un vistazo, sin recurrir a medidas eléctricas.

Una vez que tenemos el diseño verificado por simulación, lo implementaremos en la FPGA. La herramientade diseño creará un fichero de configuración (con extensión .bit). Este fichero contiene la información de laimplementación de nuestro diseño en la FPGA. Para programar la FPGA, en nuestro caso, utilizaremos uncable JTAG, que es un cable que cumple un protocolo de depuración y programación: Boundary Scan.. Estecable se conecta al puerto paralelo de nuestro ordenador.

Una vez programada la FPGA, nuestro diseño estará implementado en la FPGA y por lo tanto estará

funcionando. Dependiendo del diseño implementado, interactuará con el exterior de distinta manera ypodremos comprobar su correcto funcionamiento.

Para las prácticas utilizaremos la placa Pegasus de Digilent3, que contiene una FPGA de Xilinx de modeloSpartan-II XC2S200 con encapsulado PQ208. Esta FPGA tiene 200000 puertas lógicas equivalentes y 140 pinesdisponibles para el usuario. Con esta capacidad podemos hacer diseños digitales bastante grandes.

La placa Pegasus contiene distintos periféricos que nos facilitarán la tarea del diseño, como por ejemplo: 8LED, 4 displays de 7 segmentos, 4 botones, 8 interruptores, un puerto PS/2 (para ratón o teclado), y puertoVGA (para conectar un monitor), y varios puertos de expansión. En la figura 1.1 se muestra la placa Pegasus,y en la que se señalan varios de sus componentes. La foto de la placa no coincide exactamente con la versiónde la placa que tenemos en el laboratorio y hay algunos componentes que no están en el mismo lugar,aunque sí todos los que se han señalado.

1 http://gtebim.es2 Herramienta gratuita que se puede descargar en http://www.xilinx.com3 http://www.digilentinc.com

5/10/2018 pract_xilinx92 - slidepdf.com

http://slidepdf.com/reader/full/practxilinx92 5/94

Departamento de Tecnología Electrónica 2. Encender un LED

Diseño digital con esquemáticos y FPGA. v1.8 - 04/06/2008 4

FPGA Memoria

Flash

Display

7 segmentosLED

Pulsadores Interruptores

Conector JTAG

Jumpers de

configuración

Alimentación

VGA

PS/2

Conector

de expansión

FPGA Memoria

Flash

Display

7 segmentosLED

Pulsadores Interruptores

Conector JTAG

Jumpers de

configuración

Alimentación

VGA

PS/2

Conector

de expansión

Figura 1.1: Placa Pegasus de Digilent

A medida que vayamos avanzando con la práctica iremos aprendiendo la funcionalidad de la placa. Aún asíse puede consultar en la página web de la asignatura (http://gtebim.es/docencia/EDI) el manual de laplaca (en inglés), y una versión resumida de dicho manual en español.

Bueno, es hora ya de empezar con las practicas ...

2. Encender un LEDCuando nos enfrentamos por primera vez a diseñar mediante una metodología y herramientas nuevas, lomás aconsejable es empezar con ejemplos lo más sencillos posibles. Y a partir de éstos se irá aumentando lacomplejidad del diseño. Son muchas cosas las que pueden fallar, tanto en el uso de las herramientas de

diseño como en la placa de la FPGA. Por consiguiente, si de primeras probamos con un diseño complejo, encaso de que no funcione correctamente no sabremos si es el diseño que está mal o es algún paso que nohemos realizado bien.

De manera similar, los informáticos realizan un programa llamado "Hello world" (hola mundo), que es unprograma muy sencillo que simplemente saca por pantalla dicho texto. Nosotros, como no tenemos pantalla,encenderemos un LED. También podríamos usar el display de 7 segmentos, pero su uso es algo máscomplicado y lo que queremos es la mayor sencillez.

Ya hemos visto que la placa Pegasus tiene 8 LED disponibles para utilizar, cada uno de estos LED vanconectados a distintos pines de la FPGA, de los 140 pines que hay disponibles. La conexión de los LED semuestra en la figura 2.1. En ella se indican qué pines de la FPGA están conectados a los LED. Por ejemplo elLED número 0, está conectado al pin 46. Para facilitar esta identificación, la placa lleva impresos laidentificación del LED y el pin asociado de la FPGA. Así, podemos ver cómo al lado del LED 0 (LD0) de laplaca está el número 46 entre paréntesis. Podemos apreciar que esto se cumple para casi todos loscomponentes: pulsadores, interruptores, ...

390Ω

PIN LED

46 LD0

45 LD1

44 LD2

43 LD3

42 LD4

41 LD5

37 LD6

36 LD7

'1'→ Encendido

'0'→ Apagado

Spartan-II

390Ω

PIN LED

46 LD0

45 LD1

44 LD2

43 LD3

42 LD4

41 LD5

37 LD6

36 LD7

'1'→ Encendido

'0'→ Apagado

Spartan-II

Figura 2.1: Conexión de los LED de la placa Pegasus

Viendo el esquema eléctrico de la figura 2.1 podemos deducir que si ponemos un '1' lógico en el pin 46 de laFPGA encenderemos el LED, ya que con un '1' lógico la FPGA pondrá 3,3 voltios en ese pin (que es el nivel

5/10/2018 pract_xilinx92 - slidepdf.com

http://slidepdf.com/reader/full/practxilinx92 6/94

Departamento de Tecnología Electrónica 2. Encender un LED

Diseño digital con esquemáticos y FPGA. v1.8 - 04/06/2008 5

de tensión de ese pin de la FPGA). Por el contrario, si ponemos un '0' lógico en el pin 45, mantendremosapagado el LED 1 (LD1), puesto que no circulará corriente por él.

Así pues, éste será el objetivo del primer ejercicio, poner un '1' en el pin 46 y un '0' en el pin 45. Si después deprogramar la FPGA el LED 0 se enciende y el LED 1 se apaga habremos cumplido el objetivo. Con el resto depines que van a los otros LED no haremos nada, en teoría, haciéndolo así no deberían lucir, ya que pordefecto la FPGA pone resistencias de pull-down en los pines no configurados, y una resistencia de pull-down

pone la salida a tierra.

2.1. Diseño del circuitoEl diseño del circuito lo haremos con la herramienta ISE-Foundation o con ISE-WebPack de Xilinx, esta últimaes la versión gratuita que se puede descargar en la página web de Xilinx. Esta práctica está referida a laversión 9.2, debido a que existen nuevas versiones, puedes descargar esta versión en:http://www.xilinx.com/ise/logic_design_prod/classics.htm

Para arrancar el programa pincharemos en el icono de Xilinx o bien, desde:

Inicio→ Todos los programas→ Xilinx ISE 9.2i → Project Navigator

Nos puede aparecer una ventana con el Tip of the day que son indicaciones que hace la herramientas cada vez

que la arrancamos. Si las leemos habitualmente podemos ir aprendiendo poco a poco. Pinchamos en Ok , conlo que se cierra dicha ventana.

Normalmente la herramienta abre el último proyecto que se ha realizado. Así que lo cerramos pinchando en:File→ Close Project .

Para empezar a crear nuestro nuevo proyecto, pinchamos en File→ New Project... y nos saldrá la ventana NewProject Wizard – Create New Project como la mostrada en la figura 2.2. En ella pondremos el nombre delproyecto, que lo llamaremos led0 , indicamos la ruta donde guardaremos el proyecto(C:/practica/edi/tunombre). Respecto al nombre y a la ruta, no es conveniente trabajar desde undispositivo de memoria USB, ni tampoco incluir en la ruta o el nombre ni acentos ni eñes, ni caracteresextraños, lo más conveniente es limitarse a caracteres alfanuméricos, y usar el guión bajo en vez del espacio.Para el último recuadro de la ventana, donde pone Top-Level Source Type seleccionaremos Schematic , ya que

nuestro diseño lo haremos mediante esquemáticos.

Figura 2.2: Ventana para la creación de nuevo proyecto

Una vez que hemos rellenado los tres recuadros pinchamos en Next . Ahora nos aparece la ventana deselección del dispositivo (figura 2.4). En Product Category ponemos All . En la familia ponemos Spartan2 , quees, como ya hemos dicho, la FPGA que tenemos en la placa de Pegasus. Los siguientes datos los podemosobtener a partir de la observación del texto del encapsulado de la FPGA, que se muestran en la figura 2.3.

Hay que observar los valores que tiene la FPGA de nuestra placa, ya que en algunas el tipo es XC2S200 y enotras es XC2S50. Lo mismo sucede con la velocidad, en algunas es 5 y otras 6.

5/10/2018 pract_xilinx92 - slidepdf.com

http://slidepdf.com/reader/full/practxilinx92 7/94

Departamento de Tecnología Electrónica 2. Encender un LED

Diseño digital con esquemáticos y FPGA. v1.8 - 04/06/2008 6

XC2S200

PQ208

5C

tipo de dispositivo

encapsulado

velocidad

rango de operación

C: comercial

código de lote

código de fecha

XC2S200

PQ208

5C

tipo de dispositivo

encapsulado

velocidad

rango de operación

C: comercial

código de lote

código de fecha

Figura 2.3: Interpretación del texto del encapsulado de la FPGA

Para la selección de la herramienta de síntesis no tenemos alternativa, y para el simulador en esta práctica noes importante y lo dejamos en ISE Simulator (VHDL/Verilog). En el lenguaje de descripción de hardwarepreferido (Preferred Language) se deja el VHDL. Al terminar pinchamos en Next.

Mirar en la FPGA

Mirar en la FPGA

Mirar en la FPGA

Mirar en la FPGA

Figura 2.4: Ventana para la selección del dispositivo del nuevo proyecto

En las dos siguientes ventanas pinchamos en Next sin rellenar nada y en la última pinchamos en Finish.

Ya tenemos el proyecto creado y ahora nos disponemos a crear nuestro diseño. Para ello creamos una nuevafuente pinchando en Project → New Source.

Esto hará saltar a una nueva ventana que nos pedirá que seleccionemos el tipo de fuente que queremos crear.Como estamos trabajando en esquemáticos, seleccionamos Schematic , y nombramos al fichero led0 . Este pasose muestra en la figura 2.5. Posteriormente pinchamos en Next y en la siguiente ventana en Finish.

5/10/2018 pract_xilinx92 - slidepdf.com

http://slidepdf.com/reader/full/practxilinx92 8/94

Departamento de Tecnología Electrónica 2. Encender un LED

Diseño digital con esquemáticos y FPGA. v1.8 - 04/06/2008 7

Figura 2.5: Selección del tipo de nueva fuente

Si al terminar el proceso la herramienta nos muestra la siguiente imagen, debemos seleccionar el fichero quehemos creado (led0.sch) como se muestra en la figura 2.6. También se puede pinchando en Window → led0.sch

Seleccionar led0.sch

Seleccionar led0.sch

Figura 2.6: Selección de la ventana del fichero led0.sch

Ahora veremos el plano donde podremos dibujar el esquemático. En la figura 2.7 se muestra la apariencia dela herramienta. En ella se han movido las subventanas para tener una disposición más cómoda. Muévelas demanera que queden de una forma similar a la figura 2.7. Esta operación no siempre es fácil de realizar y aveces las subventanas se resisten a ser movidas. Otra opción es pinchar en Window → Tile Vertically . Luego, para

dejarlo como muestra la figura 2.7, habría que maximizar la subventana del plano donde se dibuja elcircuito, y seleccionar la pestaña de opciones y la pestaña de símbolos.

5/10/2018 pract_xilinx92 - slidepdf.com

http://slidepdf.com/reader/full/practxilinx92 9/94

Departamento de Tecnología Electrónica 2. Encender un LED

Diseño digital con esquemáticos y FPGA. v1.8 - 04/06/2008 8

Plano donde dibujaremos el circuito

SímbolosFuentes

Opciones

Procesos

Plano donde dibujaremos el circuito

Plano donde dibujaremos el circuito

Símbolos

SímbolosFuentes

FuentesOpciones

Opciones

Procesos

Procesos

Figura 2.7: Apariencia de la herramienta para empezar a realizar el esquema del circuito

En la figura 2.7 se han señalado algunas pestañas que utilizaremos durante el proceso de diseño y a las quese hará referencia durante el ejercicio. Así que familiarízate con sus nombres y vuelve a esta figura si durantela práctica no sabes a qué pestaña nos estamos refiriendo. Si quieres, pincha en ellas para ver el aspecto quetienen.

La ventana de opciones permite cambiar el comportamiento de la herramienta al dibujar el esquemático. Laventana de símbolos nos permite dibujar las puertas lógicas y los distintos componentes de nuestro diseño.En la ventana de fuentes se muestran los ficheros de nuestro diseño (en este caso sólo hay uno: led0.sch). Ypor último, en la ventana de procesos se indica a la herramienta los comandos que se quieren ejecutar.

Para empezar a diseñar volvemos a la ventana de símbolos. En ella, seleccionamos la categoría General ytomamos el símbolo vcc . Una vez que los hemos seleccionado podemos apreciar que el puntero del ratóncambia de forma cuando lo situamos en el plano del circuito. Si pinchamos en cualquier parte del plano sesituará el símbolo correspondiente a Vcc, que es la fuente de alimentación, y por tanto, en electrónica digitales un '1' lógico (ver la figura 2.8). A veces la herramienta tarda un poco en situarlo, así que no desesperes yno pinches varias veces con el ratón, pues colocarías varias Vcc por tu circuito.

Cuando hayas colocado tu fuente de alimentación, seguramente la veas un poco pequeña. Para ampliar lazona puedes pinchar en View → Zoom→ Zoom In (o bien pulsar F8 ).

Siempre que se haya seleccionado un símbolo, al pinchar con el ratón en el mapa del circuito se añade dichosímbolo. Esto puede resultar incómodo ya que podemos estar añadiendo componentes sin querer. Paraquitar esta opción y tener en cursor del ratón en modo de selección (con su flechita habitual) basta con pulsar

la tecla de escape (Esc ) o bien pulsar el icono de la flechita que está en la barra de herramientas .Si por error hemos incluido un símbolo más de una vez, para borrarlo vamos al modo selección (tecla Esc ) ypinchamos encima del símbolo que queramos eliminar. Éste cambiará a color rojo, y entonces o bien loborramos con la tecla Supr , o bien pinchamos con el botón derecho del ratón y del menú seleccionamosDelete. Como podrás apreciar viendo dicho menú, también puedes copiar y cortar de la misma manera quese hace en Windows.

5/10/2018 pract_xilinx92 - slidepdf.com

http://slidepdf.com/reader/full/practxilinx92 10/94

Departamento de Tecnología Electrónica 2. Encender un LED

Diseño digital con esquemáticos y FPGA. v1.8 - 04/06/2008 9

Figura 2.8: Creación de un nivel lógico alto: '1'

Ahora conectaremos dicho '1' lógico a un puerto de salida, para ello pincha en Add → I/O Marker , o bien pincha

en el icono de la barra de herramientas. Verás que la ventana de opciones cambia, en ella puedesdeterminar el tipo de puerto y cambiar la orientación del símbolo dibujado. Esto lo puedes cambiarposteriormente seleccionando el símbolo y pinchando con el botón derecho del ratón. Ahora, con el ratón tepones encima del final del cable del símbolo de la fuente (VCC) y encima de él pinchas con el ratón. Apareceráel símbolo del puerto, con un nombre similar a XLXN_1. Seguramente esté vertical, para ponerlo horizontal,selecciónalo (habiendo pulsado antes la tecla Esc ) y pulsa CTRL+R para rotarlo y CTRL+M para voltearlo,también lo puedes hacer pinchando con el botón derecho del ratón.

Como el nombre dado por la herramienta nos dice poco del puerto, le pondremos un nuevo nombre que nos

ayude a identificar el puerto. Para ello, seleccionamos el puerto y pinchando con el botón derecho del ratón,seleccionamos la opción Rename Port . En el cuadro de diálogo escribiremos LD0, que hace referencia al LED 0de la placa.

Hasta ahora, el aspecto de nuestro circuito debería ser el siguiente:

Figura 2.9: El 1-lógico conectado al puerto LD0

Ahora realizaremos el mismo proceso para conectar el puerto LD1 a un 0-lógico. Para ello, primero situamos

el símbolo de tierra en el mapa del circuito. En la ventana superior de símbolos mantenemos la selecciónGeneral y en la ventana inferior seleccionamos gnd (del inglés ground : tierra). Situamos la tierra en el mapadel circuito y posteriormente, de la misma manera que hicimos anteriormente, la conectamos a otro puertode salida. Este puerto de salida lo llamaremos LD1, haciendo referencia al LED número 1 de la placa.

Figura 2.10: Esquema final de nuestro circuito

5/10/2018 pract_xilinx92 - slidepdf.com

http://slidepdf.com/reader/full/practxilinx92 11/94

Departamento de Tecnología Electrónica 2. Encender un LED

Diseño digital con esquemáticos y FPGA. v1.8 - 04/06/2008 10

Ya tenemos nuestro primer diseño hecho. Le damos a guardar (es algo que deberías hacer de vez en cuando),y procederemos a implementarlo en la FPGA. Fíjate que cuando no has guardado, el nombre del circuito queestá en la pestaña del esquemático tiene un asterisco.

2.2. Síntesis e implementación del circuitoAhora selecciona la ventana de procesos y la ventana de fuentes (Sources). En la ventana de fuentes verifica

que el componente y el fichero que hemos creado está seleccionado: led0(led0.sch). Pincha en él una vez si noestuviese seleccionado.

Aunque a los puertos de salida les hayamos dado unos nombres referidos a los LED que vamos a utilizar, laherramienta no sabe qué pines queremos utilizar. Para indicarle a la FPGA qué pines vamos a utilizar y conqué puertos de nuestro diseño los vamos a conectar deberemos lanzar la herramienta PACE. Esto lo hacemosdesde la ventana de procesos, en ella despliega la sección que dice User Constraints, pincha dos veces en Assign

Package Pins (figura 2.11). Posteriormente nos saldrá una ventana de aviso que nos indica que para esteproceso se requiere añadir al proyecto un fichero del tipo UCF. Este tipo de ficheros son los que se usan paradefinir las conexiones de los pines de la FPGA con los puertos de nuestro diseño, y por tanto pinchamos enYes.

Figura 2.11: Selección para la asignación de pines

Ahora nos aparecerá la herramienta Xilinx PACE . En ella podemos distinguir tres subventanas, la de laderecha, tiene 2 pestañas en su parte inferior, en una se muestra la arquitectura de la FPGA y en la otra laasignación de los pines (ver figura 2.12).

En la subventana de la parte inferior izquierda hay una tabla con los nombres de nuestros puertos: LD0 y LD1.En una columna se indica la dirección de los puertos (ambos de salida: output). Y en la siguiente columna

(Loc ) debemos indicar el pin de la FPGA con el que queremos unir nuestros puertos. Ten cuidado porqueaquí hay un fallo de la herramienta, ya que si pinchas en las celdas de dicha columna aparece un menúdesplegable con los bancos de la FPGA (los pines se organizan en bancos), pero en estas celdas hay queindicar los pines y no los bancos. Así que pinchamos en dichas celdas y ponemos nosotros mismos el pin quequeremos conectar. Así, para el puerto LD0 conectamos el pin 46, para ello escribimos P46 (el mismo númeroque indica la placa añadiéndole una P). Para el puerto LD1 le asignamos el pin P45.

5/10/2018 pract_xilinx92 - slidepdf.com

http://slidepdf.com/reader/full/practxilinx92 12/94

Departamento de Tecnología Electrónica 2. Encender un LED

Diseño digital con esquemáticos y FPGA. v1.8 - 04/06/2008 11

Figura 2.12: Herramienta PACE para la asignación de pines

Le damos a guardar y nos saldrá una ventana que nos pregunta por el formato del fichero que guardará estainformación. Aunque nos es indiferente, seleccionamos la primera opción "XST Default <>" , pinchamos en OK ,cerramos la herramienta PACE y volvemos al ISE.

En la ventana de procesos, tenemos ordenados los pasos que debemos tomar: "Synthesize-XST" , "Implement

Design"

y"Generate Programming File"

. Así que con este orden, vamos a ir pinchando dos veces en cada uno deellos hasta que veamos que se pone una signo verde de correcto en ellos. Cuando se ponga en verde,pinchamos en el siguiente (puede salir en amarillo si indicando que hay advertencias -warnings- que muchasveces no son importantes). En realidad, si se ejecuta el último paso sin haber ejecutado los anteriores, laherramienta realiza todo el proceso.

Cuando tengamos todos los pasos correctamente ejecutados, la subventana de procesos debería mostrar elaspecto de la figura 2.13. Si es así, ya estamos en disposición de programar la FPGA. Puede ser que aparezcaalgún warning y que el proceso de síntesis tenga un símbolo amarillo triangular. Los warnings se pueden veren la ventana de design summary. De todos modos, en muchas ocasiones estas advertencias no son relevantes.

Figura 2.13: Aspecto de la subventana de procesos una vez que se ha sintetizado e implementado el diseñocorrectamente. En la ventana de la derecha, en el proceso de síntesis ha habido advertencias (warnings) que no

siempre son importantes, y por eso tiene un símbolo triangular de color amarillo

2.3. Programación de la FPGASi hemos llegado hasta aquí, ya habremos generado el fichero de programación de la FPGA (que tieneextensión .bit). Ahora veremos los pasos que hay que dar para programarla.

Lo primero que tenemos que hacer es quitar los tres jumpers de configuración: M0, M1 y M2 del conector J4,(ver situación en la figura 1.1). Para no perder las caperuzas conéctalos a un sólo conector dejando el otro alaire como se muestra a la derecha de la figura 2.14.

5/10/2018 pract_xilinx92 - slidepdf.com

http://slidepdf.com/reader/full/practxilinx92 13/94

Departamento de Tecnología Electrónica 2. Encender un LED

Diseño digital con esquemáticos y FPGA. v1.8 - 04/06/2008 12

Representación:

jumper

desconectado

jumper

conectado

jumper desconectado

sin perder su caperuza

su caperuzaestá perdida y

pisoteada por elsuelo del labo

Representación:

jumper

desconectado

jumper

conectado

jumper

conectado

jumper desconectado

sin perder su caperuza

su caperuzaestá perdida y

pisoteada por elsuelo del labo

Figura 2.14: Jumpers y su conexión

Cuando estos jumpers están conectados, la FPGA se programa desde la memoria flash de la placa, en la que seguarda un fichero de configuración para la FPGA. La Spartan-II es un tipo de FPGA volátil, esto es, requiereestar alimentada para mantener su configuración. Por tanto, cuando la apagamos se borra lo que hayamosprogramado. Para evitar tener que programar la FPGA desde el ordenador cada vez que encendamosnuestro sistema electrónico, se pone una memoria flash que la programa automáticamente. Si esto no fueseposible, este tipo de FPGA perdería casi toda su utilidad, ya que no serían autónomas y prácticamente sólovaldrían para hacer pruebas en el laboratorio.

Como nosotros estamos haciendo pruebas, queremos programar la FPGA desde el ordenador y no desde la

memoria flash, así que desconectamos los tres jumpers.Ahora hay que conectar el cable JTAG al puerto paralelo del ordenador y conectar el otro extremo del cableal conector JTAG de la placa (conector J2, ver figura 1.1). No debes conectarlo de cualquier manera, de lasdos posibilidades que hay, hazlo de forma que los nombres de las señales de la placa coincidan con losnombres de las señales del cable. Esto es: TMS con TMS, TDI con TDI, ... , y VDD con VDD o con VCC (éste es elúnico caso en que pueden no coincidir exactamente, depende del conector).

A continuación conectamos el cable de alimentación de la placa y lo enchufamos a la red eléctrica (y cuandolo desenchufes fíjate en que no se quede enchufado el adaptador de la clavija plana americana a clavijaredonda europea). Al enchufar la placa verás que se enciende el LED LD8.

Ya tenemos todo preparado para programar la FPGA y probar nuestro diseño. Volvemos al ordenador, alprograma ISE. Dentro de "Generate Programming File" desplegamos el menú pinchando el cuadradito con elsigno + dentro: + . Y pinchamos dos veces en "Configure Device (iMPACT)".

Esto arrancará la herramienta iMPACT, que nos mostrará un ventana en la que se ofrecen varias opciones,dejamos la opción que hay por defecto "configure devices using Boundary-Scan (JTAG)" y "Automatically connect to

a cable and identify Boudary-Scan chain" . Aceptamos pinchando en Finish.

Lo que hemos hecho es decirle a la herramienta que identifique los componentes que hay en la placa pormedio del protocolo Boundary-Scan (JTAG). Después de esto la herramienta procede a identificar a la placa ydebería encontrar dos componentes: la FPGA y la memoria flash. La FPGA la identifica como xc2s200 y lamemoria como xcf02s. A continuación nos pedirá los ficheros de programación para cada uno de loscomponentes (figura 2.15).

5/10/2018 pract_xilinx92 - slidepdf.com

http://slidepdf.com/reader/full/practxilinx92 14/94

Departamento de Tecnología Electrónica 2. Encender un LED

Diseño digital con esquemáticos y FPGA. v1.8 - 04/06/2008 13

Figura 2.15: iMPACT: componentes detectados y asignación de un fichero de configuración

Para la FPGA hay que asignar el fichero led0.bit, sabremos que está asignando el fichero a la FPGA porqueésta tendrá color verde y además la extensión del fichero es .bit (para las memorias es otro). Seleccionamos elfichero y pinchamos en Open. Inmediatamente nos saldrá una advertencia (Warning) que habla sobre elStartup Clock, esto no nos afecta y pulsamos en Ok .

Ahora nos pide el fichero de configuración de la memoria. Como no vamos a programarla, pulsamos en

Cancel .En la ventana central del iMPACT tenemos los dos componentes. Pinchando en cualquiera de ellos, losseleccionamos y se pondrán de color verde. Si pinchamos en la FPGA (xc2s200 ó xc2s50) con el botónderecho del ratón, nos saldrá un menú. Puede pasar que al pinchar no salga y que aparezca de nuevo laventana de la figura 2.15, eso es que se ha quedado el puntero del ratón enganchado; para evitarlo, pinchacon el botón izquierdo en cualquier parte de la ventana fuera de los símbolos de los chips y vuelve aintentarlo. Ahora, en el menú que aparece podemos asignar un fichero de configuración diferente oprogramar la FPGA (figura 2.16). Y esto es lo que vamos hacer, pinchamos en Program, y le damos a Ok a lasiguiente ventana sin cambiar nada (si diésemos a Verify daría un error de programación).

Figura 2.16: Orden para programar la FPGA

5/10/2018 pract_xilinx92 - slidepdf.com

http://slidepdf.com/reader/full/practxilinx92 15/94

Departamento de Tecnología Electrónica 2. Encender un LED

Diseño digital con esquemáticos y FPGA. v1.8 - 04/06/2008 14

Después de la orden de programar la FPGA, aparece un cuadro que muestra la evolución y, si todo ha salidobien, la herramienta nos avisará de que hemos tenido éxito en la programación mostrando un aviso como elde la figura

Figura 2.17: Programación realizada con éxito

Ahora miramos la placa y debería haber tres LED encendidos:• LD8: que indica que la placa está encendida• LD9: que indica que se ha programado la FPGA• LD0: que es el LED que hacemos encender nosotros con el diseño de la FPGA

El LED LD1 deberá estar apagado, pues lo hemos puesto a un '0' lógico. Y el resto de LED también estaránapagados debido a las resistencias de pull-down que la FPGA pone en los puertos sin conectar.

Con esto hemos terminado el primer ejercicio. Hemos comprobado que la placa y la herramienta funcionan,y ya podemos probar otros diseños más complejos.

5/10/2018 pract_xilinx92 - slidepdf.com

http://slidepdf.com/reader/full/practxilinx92 16/94

Departamento de Tecnología Electrónica 3. Puertas lógicas, interruptores y

pulsadores

Diseño digital con esquemáticos y FPGA. v1.8 - 04/06/2008 15

3. Puertas lógicas, interruptores y pulsadoresEn este ejercicio vamos diseñar un circuito sencillo con el que podamos interactuar. Para ello usaremos comoentradas del circuito los interruptores y pulsadores de la placa. Además incluiremos alguna lógica interna.

A partir de ahora no se va a realizar una explicación tan detallada como la del primer ejercicio, si durante laejecución de este ejercicio has olvidado algún paso, repasa lo explicado en el ejercicio anterior.

Analizando las conexiones de los interruptores (figura 3.1) vemos que cuando el interruptor está hacia arribatransmite un 1-lógico a la entrada de la FPGA. En la placa, a la derecha del interruptor SW0 se indica quehacia arriba son 3,3V y hacia abajo son 0V.

4,7kΩ

PIN interruptor

89 SW0

88 SW187 SW2

86 SW384 SW4

83 SW5

82 SW681 SW7

Spartan-II3,3V

4,7kΩ

PIN pulsador

59 BTN058 BTN1

57 BTN2154 BTN3

Spartan-II3,3V

4,7kΩ 0,1μF

4,7kΩ

PIN interruptor

89 SW0

88 SW187 SW2

86 SW384 SW4

83 SW5

82 SW681 SW7

Spartan-II3,3V

4,7kΩ

PIN pulsador

59 BTN058 BTN1

57 BTN2154 BTN3

Spartan-II3,3V

4,7kΩ 0,1μF

Figura 3.1: Esquema eléctrico de las conexiones de los interruptores y pulsadores en la placa Pegasus

Para los pulsadores, cuando están pulsados transmiten un 1-lógico a la entrada y cuando no están pulsadosponen 0 voltios a la entrada. Observa que los pulsadores tienen un pequeño circuito con resistencias y uncondensador, esto es para eliminar los rebotes que se producen al pulsar y así enviar una señal sin ruido.

3.1. Diseño del circuitoCreamos un nuevo proyecto (File→ New Proyect...) llamado swt0 con las mismas características que el anterior.Creamos una nueva fuente de tipo esquemático llamada swt0.sch. Y tendremos una pantalla similar a la dela figura 2.7.

Como vamos a realizar el circuito con puertas lógicas, en la subventana de categorías (Categories) dentro de la

ventana de símbolos, seleccionamos el elemento Logic . Veremos como en la subventana de símbolos (Symbols)aparecen nombres relativos a puertas lógicas (and12, and16, and2, or2, ...) el número indica el número deentradas de la puerta y si hay alguna b indica que tiene una entrada negada. La figura 3.2 muestra ejemplosde esta nomenclatura.

and2b1

AND de 2 entradas con

una de ellas negada

and3b2

AND de 3 entradas con

dos de ellas negadas

and2

AND de 2 entradas

and2b1

AND de 2 entradas con

una de ellas negada

and2b1

AND de 2 entradas con

una de ellas negada

and3b2

AND de 3 entradas con

dos de ellas negadas

and3b2

AND de 3 entradas con

dos de ellas negadas

and2

AND de 2 entradas

and2

AND de 2 entradas

Figura 3.2: Ejemplos de la nomenclatura de las puerta lógicas

Lo primero que haremos es añadir una puerta AND (and2

) en el mapa y conectamos sus entradas y salidascon puertos ( Add → I/O Marker ). Los puertos de entrada los llamaremos SW0 y SW1, que se corresponderán conlos interruptores 0 y 1. Y el puerto de salida lo renombraremos como LD0, que será el LED número cero.Quedando como muestra la figura 3.3.

Figura 3.3: Implementación de la puerta AND

De manera similar conectaremos los interruptores SW2 y SW3 con la entrada de una puerta OR, y su salida laconectaremos a LD1, obteniendo algo similar a la figura 3.4.

5/10/2018 pract_xilinx92 - slidepdf.com

http://slidepdf.com/reader/full/practxilinx92 17/94

Departamento de Tecnología Electrónica 3. Puertas lógicas, interruptores y

pulsadores

Diseño digital con esquemáticos y FPGA. v1.8 - 04/06/2008 16

Figura 3.4: Implementación de la puerta OR

Ahora conectaremos un inversor al pulsador BTN0 y su salida la conectaremos a LD2:

Figura 3.5: Implementación de un inversor

Además queremos conectar la entrada del pulsador BTN0 a LD3. Como no podemos conectar directamente elpuerto de entrada BTN0 al puerto de salida LD3, los conectamos mediante un buffer . Para ello, en lasubventana de categorías (Categories) seleccionamos Buffer . Para el símbolo seleccionamos buf y lo situamosencima del inversor (fíjate que el símbolo es el mismo pero sin la bolita a la salida, por eso no invierte).Conectamos la salida del buffer al LED LD3.

Figura 3.6: Buffer que queremos conectar a la misma entrada (BTN0) que la del inversor

Para conectar la entrada del buffer al puerto de entrada BTN0 necesitamos un cable. Los cables los

implementan pinchando en Add → Wire, o bien con el icono , o bien tecleando CTRL+W . Una vez que hemosseleccionado este comando, veremos que en la ventana de opciones aparecen las opciones para situar loscables. En ella seleccionamos la primera opción: Use the Autorouter to add one o more line segments between the points you indicate. Y posteriormente pinchamos al cable que está entre la salida del puerto BTN0 y la entradadel inversor; sin soltar el botón del ratón, nos dirigimos a la entrada del buffer . Puede pasar que laherramienta dé un mensaje que diga: The pin 'I' is already connected to a net. Only one net is allowed to connect to

a pin. Con esto quiere decir que sólo se puede conectar un cable a un pin. Pero lo que sí se puede hacer esconectarlo al cable que une el pin con la entrada del inversor. Puede ser que tengas poco espacio entre el piny la entrada del inversor. Para alargar ese cable, puedes seleccionar y arrastrar el pin de entrada a laizquierda. Ahora será más fácil conectar la entrada del buffer con el cable.

Figura 3.7: Conexión final del buffer e inversor

Nuestro diseño final tiene 3 entradas (SW0, SW1 y BRN0) y 4 salidas (LD0, LD1, LD2 y LD3). Y deberá tener el

siguiente aspecto:

Figura 3.8: Diseño final del ejercicio

5/10/2018 pract_xilinx92 - slidepdf.com

http://slidepdf.com/reader/full/practxilinx92 18/94

Departamento de Tecnología Electrónica 3. Puertas lógicas, interruptores y

pulsadores

Diseño digital con esquemáticos y FPGA. v1.8 - 04/06/2008 17

Para comprobar que hemos hecho la conexión bien podemos pinchar en Tools→ Check Schematic, y revisamos

la ventana inferior ( Console) para ver si ha detectado algún error o advertencia.

Grabamos el esquemático: File→ Save (esto deberías hacerlo regularmente).

Debido a que es un diseño pequeño podríamos probar el circuito directamente en la placa, sin embargovamos a simularlo antes para aprender el proceso.

3.2. Simulación del circuitoUna vez que hemos terminado el esquemático y lo hemos grabado, seleccionamos la ventana de fuentes

( Sources) y la ventana de procesos ( Processes).

En la parte superior de la ventana de fuentes, vemos que indica Sources for: "Synthesis/Implementation" (verfigura 3.9). El menú desplegable permite seleccionar el tipo de ficheros fuente con los que se quiere trabajar:para simulación o para síntesis. Es importante conocer esta opción, debido a que nos puede ocurrir que noveamos un fichero que hemos creado a causa de tener seleccionada una opción que no lo muestra. Porejemplo, los ficheros para simulación no se verán en caso de tener seleccionada la opción de síntesis.

Selección de fuentes para:

- Síntesis/Implementación- Simulación comportamental

- Simulación post-rutado

Selección de fuentes para:

- Síntesis/Implementación- Simulación comportamental

- Simulación post-rutado

Figura 3.9: Selección de los ficheros fuente según el tipo de actividad que se vaya a realizar

Como ahora queremos simular el circuito para comprobar su funcionamiento, seleccionamos Sources for:

"Behavioural Simulation" . Como resultado de esta selección, la ventana de procesos

cambia. Por lo tanto, si encualquier momento ves que la ventana de procesos no está como piensas que debería estar, comprueba quehas seleccionado el menú de fuentes adecuado. Por ejemplo, puede pasar que quieras sintetizar el diseño yno aparezca el comando, entonces mira qué opción tienes seleccionada.

Ahora crearemos un nuevo fichero para simular nuestro diseño. Mediante un cronograma, este ficheroindicará al simulador qué valores toman las entradas en función del tiempo. En la ventana de procesos pinchamos dos veces en Create New Source. Y nos saldrá una ventana como la de la figura 3.10, que es similara la que ya vimos en la figura 2.5.

Figura 3.10: Creación de una fuente para la simulación

Tal como se muestra en la figura 3.10, seleccionamos el tipo de fichero como Test Bench Waveform. Lonombramos tb_swt0 y pinchamos en Next . Test Bench significa "banco de pruebas", y eso es lo que queremoshacer, un banco de pruebas que demuestre que el diseño funciona como queremos. Waveform significa

5/10/2018 pract_xilinx92 - slidepdf.com

http://slidepdf.com/reader/full/practxilinx92 19/94

Departamento de Tecnología Electrónica 3. Puertas lógicas, interruptores y

pulsadores

Diseño digital con esquemáticos y FPGA. v1.8 - 04/06/2008 18

"forma de onda", así que nuestro banco de pruebas lo definiremos con las formas de onda de los puertos deentrada (ahora veremos cómo y por qué).

La siguiente ventana nos pide que seleccionemos el diseño que vamos a probar con el banco de pruebas. Ennuestro caso solo hay uno: swt0 . Y así que pinchamos en Next y en la siguiente ventana en Finish.

Surgirá una ventana que nos pide mucha información (figura 3.11). Como nuestro circuito no tiene reloj nielementos de memoria (ya los estudiaremos en el tema 7) es un circuito combinacional, y por tanto, en elapartado de Clock Information, seleccionamos Combinatorial (or internal clock). Además, deseleccionamos lacasilla GSR (FPGA) y el resto de opciones las dejamos como están y pinchamos en Finish.

Figura 3.11: Opciones de la temporización de la simulación

Y así llegamos a una ventana como la de la figura 3.12 en la que en la vertical se muestran los puertos deentrada y salida, y en la horizontal un eje de tiempos. En medio de estos dos ejes tendremos los valores delas señales según el tiempo en que estemos.

Puertos de entrada

Puertos de entradaEje temporal

Eje temporal

Valores de las señales en el tiempo

Valores de las señales en el tiempoPuertos de salida

Puertos de salida

Puertos de entrada

Puertos de entradaEje temporal

Eje temporal

Valores de las señales en el tiempo

Valores de las señales en el tiempoPuertos de salida

Puertos de salida

Figura 3.12: Ventana de los cronogramas de las señales de simulación

5/10/2018 pract_xilinx92 - slidepdf.com

http://slidepdf.com/reader/full/practxilinx92 20/94

Departamento de Tecnología Electrónica 3. Puertas lógicas, interruptores y

pulsadores

Diseño digital con esquemáticos y FPGA. v1.8 - 04/06/2008 19

Ahora nosotros tenemos que asignar los valores de los puertos de entrada, para que a partir de ellos elsimulador calcule los de salida. Inicialmente, la ventana asigna a todos los puertos de entrada el valor '0'.Nosotros vamos a asignar diversos valores para comprobar el funcionalidad de nuestro circuito en distintoscasos.

Antes de asignar los valores, vamos a agrupar las señales entre sí, para comprobar de manera más fácil losresultados de la simulación. SW0 y SW1 van a las entradas de una puerta AND cuya salida es LD0. Así que las

vamos a poner juntas. Esto se hace pinchando en el nombre del puerto y arrastrándolo hasta dondequeramos. Hacemos lo mismo con el resto: SW2, SW3 y LD1 juntas; y por último BTN0 junto con LD2 y LD3.

Pinchando en los recuadros azules del cronograma de los puertos de entrada modificamos su valor. El anchode estos cuadrados se define en la ventana de la figura 3.11, nosotros los dejaremos con su valor por defecto.

Como tenemos un diseño pequeño, los valores de las entradas que vamos a asignar cubrirán todas lasposibilidades para cada puerta. Así, haremos que las entradas SW0 y SW1, de la puerta AND, tomen todos losvalores de la tabla de verdad. En la figura 3.13 se muestran los valores que se quieren asignar a los puertosde entrada y los intervalos de tiempo en que se asignarán. También se muestra los valores que deben salir(los valores de los LED) y que más adelante comprobaremos si coinciden con los de la simulación.

tiempo SW0 SW1 LD0

0-100ns 0 0 0100-200 0 1 0

200-300 1 0 0

300-400 1 1 1

LD0: AND

tiempo SW2 SW3 LD1

0-100ns 0 0 0100-200 0 1 1

200-300 1 0 1

300-400 1 1 1

LD1: OR

tiempo BTN0 LD2 LD3

0-200ns 0 1 0200-400 1 0 1

LD2: NOT

tiempo SW0 SW1 LD0

0-100ns 0 0 0100-200 0 1 0

200-300 1 0 0

300-400 1 1 1

LD0: AND

tiempo SW2 SW3 LD1

0-100ns 0 0 0100-200 0 1 1

200-300 1 0 1

300-400 1 1 1

LD1: OR

tiempo BTN0 LD2 LD3

0-200ns 0 1 0200-400 1 0 1

LD2: NOT

Figura 3.13: Asignación de valores a los puertos de entrada de modo que cubran todas las posibilidades de la tabla de

verdad

Asignando los valores de la figura 3.13 obtendremos un cronograma como el mostrado en la figura 3.14.Cuando lo tengamos hecho lo grabamos y comprobaremos cómo aparece en la ventana de fuentes:tb_swt0.tbw, y cómo dentro de él está nuestro diseño4: UUT – swt0(swt0.sch).

Figura 3.14: Valores en los puertos de entrada para la simulación

Para simularlo, en la ventana de fuentes (Sources) el fichero tb_swt0.tbw debe estar seleccionado, y en laventana de Procesos, dentro de Xilinx ISE Simulator , pincharemos dos veces en Simulate Behavioral Model . Estodará la orden para llevar a cabo la simulación, y finalmente obtendremos los resultados de la simulación enel cronograma (figura 3.15). Las señales se pueden haber descolocado y las volvemos a colocar en el mismoorden. Ahora debemos comprobar que los valores a las salidas se corresponden con los valores queesperamos (los de la figura 3.13).

Para comprobar el buen funcionamiento de LD0 vemos que está a '1' sólo cuando SW0 y SW1 están a '1'. Esto esasí porque es una AND. Para la LD1, como es una OR, valdrá '1' cuando SW2 o SW3 sean '1'. Y por último,vemos que LD2 y LD3 tienen valores complementarios, ya que LD2 invierte el valor de BTN0 y LD1 lo asigna

directamente. Así pues, se cumple lo que habíamos esperado en la figura 3.13.

4 UUT indica el componente que se está comprobando, es el acrónimo del inglés: Unit Under Test

5/10/2018 pract_xilinx92 - slidepdf.com

http://slidepdf.com/reader/full/practxilinx92 21/94

Departamento de Tecnología Electrónica 3. Puertas lógicas, interruptores y

pulsadores

Diseño digital con esquemáticos y FPGA. v1.8 - 04/06/2008 20

Figura 3.15: Resultados de la simulación

Después de haber comprobado la funcionalidad del circuito, nos disponemos a implementarlo en la FPGA

3.3. Síntesis e implementación del circuitoLos pasos que debemos tomar son casi los mismos que los que tomamos en el ejemplo anterior. Aunqueahora, como venimos de la simulación, lo primero que tienes que hacer es seleccionar en la ventana defuentes

las fuentes para síntesis: Sources for: "Synthesis/Implementation" (ver figura 3.9). Debemos tambiénactivar la ventana de procesos, que es donde le indicaremos a la herramienta que comandos de síntesis debeejecutar (recuerda la figura 2.7).

Antes de dar la orden de sintetizar debes asignar los pines de la FPGA. Ahora tenemos más pines queasignar. Repite el mismo proceso y asigna los pines conforme a la numeración de la placa (si se te haolvidado, vuelve a mirarte el ejercicio anterior).

Ya podemos sintetizar e implementar el circuito y pasarlo a la placa. Si todo ha salido bien, podráscomprobar que los LED de la placa se enciende en función del estado de los interruptores y el pulsador 0.

5/10/2018 pract_xilinx92 - slidepdf.com

http://slidepdf.com/reader/full/practxilinx92 22/94

Departamento de Tecnología Electrónica 4. Decodificador de 2 a 4

Diseño digital con esquemáticos y FPGA. v1.8 - 04/06/2008 21

4. Decodificador de 2 a 4En este ejercicio implementaremos un decodificador de 2 a 4 como los que hemos visto en clase. Undecodificador de 2 a 4 recibe dos entradas que están codificadas en binario y según que número estécodificado activa la salida correspondiente a ese número. Por ejemplo, si el número de la entrada es 102,activará la salida 2, ya que 102 es dos en binario. Además, los decodificadores suelen tener una señal de

habilitación (enable

) que en caso de no estar activa, todas las salidas estarán también inactivasindependientemente del valor del resto de entradas.

Por tanto, nuestro decodificador será un bloque como el mostrado en la figura 4.1, cuya tabla de verdadtambién se muestra.

A0

A1

S0

S1

S2

S3E

DECOD 2a4

E A1 A0 S3 S2 S1 S0

0 X X 0 0 0 0

1 0 0 0 0 0 1

1 0 1 0 0 1 0

1 1 0 0 1 0 0

1 1 1 1 0 0 0

A0

A1

S0

S1

S2

S3E

DECOD 2a4

E A1 A0 S3 S2 S1 S0

0 X X 0 0 0 0

1 0 0 0 0 0 1

1 0 1 0 0 1 0

1 1 0 0 1 0 0

1 1 1 1 0 0 0

E A1 A0 S3 S2 S1 S0

0 X X 0 0 0 0

1 0 0 0 0 0 1

1 0 1 0 0 1 0

1 1 0 0 1 0 0

1 1 1 1 0 0 0

Figura 4.1: Decodificador de 2 a 4 y su tabla de verdad

4.1. Diseño del decodificador Si nos fijamos en la tabla de verdad del decodificador (figura 4.1), considerando que E=1, podemos ver quecada una de las salidas S0, S1, S2 y S3, se corresponde con un término mínimo de A1 y A0. Por ejemplo, la

salida S0 es el término mínimo 0 (m0=A1 ⎯⎯ ·A0 ⎯⎯ ); la salida S1 es el término mínimo 1 (m1=A1 ⎯⎯ ·A0), y de manerasimilar para el resto.

Luego sólo tendremos que añadir la habilitación y obtendremos las salidas.

Empecemos a diseñar: primero creamos un nuevo proyecto llamado decod2a4 en el directorioC:/practica/edi/tunombre. Recuerda no poner tildes ni eñes, y mejor si no pones espacios. El proyecto debetener las mismas características de los proyectos anteriores. Creamos también una nueva fuente con elmismo nombre y de tipo esquemático (Schematic). Ya tendremos que tener el plano vacío de nuestro circuito.

Ya que el decodificador implementa todos los términos mínimos, necesitaremos todas las entradas negadas yafirmadas (no negadas). Como los puertos no se pueden colocar solos (se deben conectar a las patas de algúncomponente), empezamos colocando los dos inversores de las entradas A1 y A0. Y posteriormente lesconectamos los puertos de entrada (figura 4.2).

Figura 4.2: Inversores colocados a las entradas para formar los términos mínimos

Ahora conectamos un cable a la salida de cada inversor (mediante el icono ). El otro lado del cable lo

dejamos al aire: pinchamos en un punto más alejado a la derecha y pulsamos la tecla ESC . El extremo delcable tendrá un cuadradito rojo que indica que sin conectar (al aire).

Vamos a nombrar los terminales de cada cable que hemos dejado al aire. Seleccionamos Add → Net Name

(también hay un icono ). Y en la ventana de opciones, en el apartado Name ponemos el nombre del cable.Para el negado de A1 lo llamamos N_A1, y el negado de A0 lo llamamos N_A0. Para colocarlo nos ponemos alfinal del cable y pinchamos encima. Para colocar el segundo, cambiamos el nombre y repetimos la operación.

Llegados a este punto, deberíamos tener:

Figura 4.3: Inversores con nombre a la salida

5/10/2018 pract_xilinx92 - slidepdf.com

http://slidepdf.com/reader/full/practxilinx92 23/94

Departamento de Tecnología Electrónica 4. Decodificador de 2 a 4

Diseño digital con esquemáticos y FPGA. v1.8 - 04/06/2008 22

A continuación incluiremos 4 puertas AND de dos entradas que se encargarán de crear los 4 términosmínimos. Por ahora simplemente las creamos una debajo de la otra, y conectamos un cable a la salida decada una de ellas.

Figura 4.4: Inversores y las cuatro puertas AND para formar los términos mínimos

Ahora vamos a conectar las entradas de cada una de las puertas. La puerta de arriba será la del términomínimo cero (m0) y la de abajo m3. Para unir los cables de los puertos de entrada (negados o no) con lasentradas de las puertas usamos el comando Add → Net¸ y dejamos la opción por defecto: Use the Autorouter to addone or more line segments between the points you indicate. Al unir los cables veremos que en las uniones se formaun cuadradito que indica la conexión entre cable. Al terminar de unir los cables tendremos un circuito como

el siguiente. Si te equivocas, usa CTRL+Z para deshacer la última unión.

Figura 4.5: Términos mínimos del decodificador

Añade también los nombres de cada uno de los términos mínimos (como se ve en la figura 4.5). Para facilitarla tarea, puedes empezar por m0, y si seleccionas dentro de la ventana de opciones, en el apartado que indica After naming the branch or net marcas la opción: Increase the name; el índice de término mínimo se

incrementará por sí solo.Ahora sólo nos queda incluir la señal de habilitación. Cuando ésta es cero, las salidas son cero, por tanto sepuede añadir al final de cada término mínimo mediante una puerta AND. Recuerda que la puerta AND

5/10/2018 pract_xilinx92 - slidepdf.com

http://slidepdf.com/reader/full/practxilinx92 24/94

Departamento de Tecnología Electrónica 4. Decodificador de 2 a 4

Diseño digital con esquemáticos y FPGA. v1.8 - 04/06/2008 23

actúa como una compuerta en el sentido que si E='0' la salida vale '0' (inhabilitada) y si E='1' la salida vale loque la otra entrada (ver figura 4.6).

E

m0S0

E='0'

m0S0='0'

E='0'→ Salida inhabilitada

E='1'

m0S0=m0

E='1'→ Salida habilitadaE→ Habilitación

E

m0S0

E='0'

m0S0='0'

E='0'→ Salida inhabilitada

E='1'

m0S0=m0

E='1'→ Salida habilitadaE→ Habilitación

Figura 4.6: Puerta AND como habilitación

Añadimos las puertas y las conectamos con la señal de habilitación. El circuito debería quedarnos como lasiguiente figura

Figura 4.7: Esquema de puertas del decodificador

Antes de seguir, debemos guardar el fichero (CRTL+S ) y comprobar si todas las conexiones están bienhechas: Tools→ Check Schematic . Debemos ver los errores o advertencias que puedan aparecer en la consola(ventana de abajo). Si hubiese algún error, debemos comprobar qué cable o componente se trata, moverlopara ver si realmente está conectado y conectarlo bien. Vuelve a comprobar el esquemático (Tools→ Check

Schematic ) cuantas veces haga falta hasta que no tengas errores, y el final guarda el fichero.

4.2. Comprobación del diseñoAntes de implementarlo en la placa vamos a ver si está bien diseñado. Para ello seguimos los mismos pasosque en el apartado 3.2:

• Seleccionamos en la ventana de fuentes (Sources) la opción de Behavioural Simulation

• En la ventana de procesos pinchamos en Create New Source • Seleccionamos el tipo: Test Bench Waveform, y nombramos el fichero tb_decod2a4 • En la ventana de las opciones del cronograma (figura 3.11) indicamos que es un diseño combinacional y

deseleccionamosGSR (FPGA), que está dentro Global Signals. Para terminar pinchamos en Finish. • Introducimos en el cronograma los valores de las entradas y guardamos el fichero del banco de pruebas• Damos la orden de simular Simulate Behavioral Model .• Comprobamos si los valores a las salidas son correctos.

Como sólo tenemos 3 entradas, introduciremos las 8 combinaciones posibles. Éstas se muestran en la figura4.8.

5/10/2018 pract_xilinx92 - slidepdf.com

http://slidepdf.com/reader/full/practxilinx92 25/94

Departamento de Tecnología Electrónica 4. Decodificador de 2 a 4

Diseño digital con esquemáticos y FPGA. v1.8 - 04/06/2008 24

Figura 4.8: Valores introducidos en el cronograma para la simulación del decodificador

Después de la simulación, los resultados de las salidas son:

Figura 4.9: Cronograma de la simulación

Podemos ver que los resultados de la simulación son correctos. Cuando E='0' no hay ninguna salida activa,y cuando E='1' se van activando las distintas salidas según cambian las entradas.

4.3. Implementación del diseñoAhora pasamos a implementarlo en el FPGA, si no te acuerdas, repasa lo visto en el apartado 2.2. Aquí terecordamos los pasos principales:

• Como venimos de la simulación, lo primero que tienes que hacer es seleccionar en la ventana de fuentes las

fuentes para síntesis: Sources for: "Synthesis/Implementation" (ver figura 3.9).• Activa la ventana de procesos, que es donde le indicaremos a la herramienta que comandos de síntesis debe

ejecutar (recuerda la figura 2.7).• Asigna los pines de la FPGA. Asigna el puerto A0 al interruptor SW0, el puerto A1 al interruptor SW1, y la

habilitación a el interruptor SW7. Los 4 LED de salida asígnalos consecutivamente.• Sintetiza e implementa el diseño• Comprueba que funciona como debe funcionar

4.4. Creación de un bloqueSi hemos llegado hasta aquí significa que nuestro diseño funciona bien, tanto en simulación comofísicamente en la placa, ahora vamos a crear un módulo que integre este codificador para que cada vez que

lo necesitemos implementar en diseños más grandes, no tengamos que crear todo el esquema de puertas sinoque conectaremos un bloque como el de la figura 4.1. Sería similar a un componente MSI ( Medium ScaleIntegration) como los chips disponibles para diseño con componentes discretos. Por ejemplo losdecodificadores 74LS138 y 74LS139.

Esto nos permitirá subir el nivel de abstracción y diseñar con bloques lógicos en vez de con puertas, lo quehará que podamos diseñar de manera más rápida y con menos probabilidad de equivocarnos, ya que cadauno de los bloques están probados y sabemos que funcionan correctamente.

Volvemos a la vista del mapa del circuito: dentro de la ventana de fuentes pinchamos dos veces en eldecodificador (decod2a4) o bien seleccionándolo directamente en la pestaña de la ventana grande.

Para crear el módulo (Xilinx lo llama símbolo) pinchamos en Tools→ Symbol Wizard , lo que hará que aparezcauna ventana (figura 4.10) que nos preguntará para qué componente vamos a crear un símbolo. En la opción

Pin Name Source, seleccionamos Using Schematic , y aparecerá el único esquemático que hemos creado en esteproyecto: decod2a4.

5/10/2018 pract_xilinx92 - slidepdf.com

http://slidepdf.com/reader/full/practxilinx92 26/94

Departamento de Tecnología Electrónica 4. Decodificador de 2 a 4

Diseño digital con esquemáticos y FPGA. v1.8 - 04/06/2008 25

Figura 4.10: Selección del componente para el que vamos a crear un símbolo

Pinchamos en Next y aparecerá una ventana con las entradas y salidas del módulo. En ella podemos cambiarel lugar donde aparecerán (derecha o izquierda) y el orden. Ponemos el mismo orden de la figura 4.11.

Figura 4.11: Determinación de la posición de los pines del símbolo

Pinchando en Next la siguiente ventana nos preguntan por las distancias y los tamaños del símbolo. Lodejamos como está, o bien, si lo prefieres de otra manera, puedes modificarlo a tu gusto. Volvemos a pincharen Next , y tendremos una ventana con el símbolo de nuestro decodificador (figura 4.12). Si nos gustapinchamos en Finish.

5/10/2018 pract_xilinx92 - slidepdf.com

http://slidepdf.com/reader/full/practxilinx92 27/94

Departamento de Tecnología Electrónica 4. Decodificador de 2 a 4

Diseño digital con esquemáticos y FPGA. v1.8 - 04/06/2008 26

Figura 4.12: Aspecto final del símbolo de nuestro decodificador

Por último tendremos el decodificador en el editor de esquemáticos (figura 4.13), en donde hay una pestañapara acceder al esquema en puertas.

Esquema en puertas

Esquema en puertas Símbolo

Símbolo

Esquema en puertas

Esquema en puertas Símbolo

Símbolo

Figura 4.13: Símbolo del decodificador en el editor de esquemáticos

Ahora podremos utilizar este símbolo en otros diseños. En esto va a consistir el próximo ejercicio.

5/10/2018 pract_xilinx92 - slidepdf.com

http://slidepdf.com/reader/full/practxilinx92 28/94

Departamento de Tecnología Electrónica 5. Decodificador de 3 a 8

Diseño digital con esquemáticos y FPGA. v1.8 - 04/06/2008 27

5. Decodificador de 3 a 8Hemos realizado el decodificador de 2 a 4, utilizando dos interruptores encendíamos uno de los cuatroprimeros LED. Ahora vamos a construir un decodificador que encienda uno de los 8 LED, utilizaremos paraello los tres primeros interruptores.

Aunque este ejercicio ya se ha explicado en clase, vamos a repasarlo un poco. En la figura 5.1 se muestra el

bloque final que queremos obtener y la tabla de verdad. La tabla de verdad es muy similar a la delcodificador de 2 a 4 (figura 4.1).

Podríamos hacer el ejercicio de la misma manera que el decodificador de 2 a 4, sin embargo, si lo hacemosuniendo dos decodificadores de 2 a 4 lograremos diseñarlo de manera mucho más rápida y entendible. Esdifícil de entender el funcionamiento de un diseño grande en puertas, mientras que si lo hacemos conbloques es más claro.

A0

A1

S0

S1

S2

S3

E

D E

C O D

3 a

8

S4

S5

S6

S7

A2

E A2 A1 A0 S7 S6 S5 S4 S3 S2 S1 S0

0 X X X 0 0 0 0 0 0 0 01 0 0 0 0 0 0 0 0 0 0 11 0 0 1 0 0 0 0 0 0 1 0

1 0 1 0 0 0 0 0 0 1 0 0

1 0 1 1 0 0 0 0 1 0 0 01 1 0 0 0 0 0 1 0 0 0 01 1 0 1 0 0 1 0 0 0 0 01 1 1 0 0 1 0 0 0 0 0 0

1 1 1 1 1 0 0 0 0 0 0 0

A0

A1

S0

S1

S2

S3

E

D E

C O D

3 a

8

S4

S5

S6

S7

A2

E A2 A1 A0 S7 S6 S5 S4 S3 S2 S1 S0

0 X X X 0 0 0 0 0 0 0 01 0 0 0 0 0 0 0 0 0 0 11 0 0 1 0 0 0 0 0 0 1 0

1 0 1 0 0 0 0 0 0 1 0 0

1 0 1 1 0 0 0 0 1 0 0 01 1 0 0 0 0 0 1 0 0 0 01 1 0 1 0 0 1 0 0 0 0 01 1 1 0 0 1 0 0 0 0 0 0

1 1 1 1 1 0 0 0 0 0 0 0

E A2 A1 A0 S7 S6 S5 S4 S3 S2 S1 S0

0 X X X 0 0 0 0 0 0 0 01 0 0 0 0 0 0 0 0 0 0 11 0 0 1 0 0 0 0 0 0 1 0

1 0 1 0 0 0 0 0 0 1 0 0

1 0 1 1 0 0 0 0 1 0 0 01 1 0 0 0 0 0 1 0 0 0 01 1 0 1 0 0 1 0 0 0 0 01 1 1 0 0 1 0 0 0 0 0 0

1 1 1 1 1 0 0 0 0 0 0 0

Figura 5.1: Esquema del decodificador de 3 a 8 y su tabla de verdad

Si analizamos la tabla de verdad y la dividimos en tres partes según los valores de E y A2 (figura 5.2),podemos ver que:

• Cuando E=0, el circuito está inactivo• Cuando E=1, y A2=0, las señales S7 a S4 están inactivas, y las señales S3 a S0 se comportan igual que el

decodificador de 2 a 4.• Cuando E=1, y A2=1, las señales S3 a S0 están inactivas, y las señales S7 a S4 se comportan igual que el

decodificador de 2 a 4.

E A2 A1 A0 S7 S6 S5 S4 S3 S2 S1 S0

1 0 0 0 0 0 0 0 0 0 0 1

1 0 0 1 0 0 0 0 0 0 1 0

1 0 1 0 0 0 0 0 0 1 0 0

1 0 1 1 0 0 0 0 1 0 0 0

A2 = '1'

E A2 A1 A0 S7 S6 S5 S4 S3 S2 S1 S0

0 X X X 0 0 0 0 0 0 0 0

A2 = '0'

todas '0' igual que decod2a4

E A2 A1 A0 S7 S6 S5 S4 S3 S2 S1 S0

1 1 0 0 0 0 0 1 0 0 0 0

1 1 0 1 0 0 1 0 0 0 0 0

1 1 1 0 0 1 0 0 0 0 0 0

1 1 1 1 1 0 0 0 0 0 0 0

todas '0'igual que decod2a4

todas '0'

misma

secuencia

E A2 A1 A0 S7 S6 S5 S4 S3 S2 S1 S0

1 0 0 0 0 0 0 0 0 0 0 1

1 0 0 1 0 0 0 0 0 0 1 0

1 0 1 0 0 0 0 0 0 1 0 0

1 0 1 1 0 0 0 0 1 0 0 0

A2 = '1'

E A2 A1 A0 S7 S6 S5 S4 S3 S2 S1 S0

0 X X X 0 0 0 0 0 0 0 0

E A2 A1 A0 S7 S6 S5 S4 S3 S2 S1 S0

0 X X X 0 0 0 0 0 0 0 0

A2 = '0'

todas '0' igual que decod2a4

E A2 A1 A0 S7 S6 S5 S4 S3 S2 S1 S0

1 1 0 0 0 0 0 1 0 0 0 0

1 1 0 1 0 0 1 0 0 0 0 0

1 1 1 0 0 1 0 0 0 0 0 0

1 1 1 1 1 0 0 0 0 0 0 0

E A2 A1 A0 S7 S6 S5 S4 S3 S2 S1 S0

1 1 0 0 0 0 0 1 0 0 0 0

1 1 0 1 0 0 1 0 0 0 0 0

1 1 1 0 0 1 0 0 0 0 0 0

1 1 1 1 1 0 0 0 0 0 0 0

todas '0'igual que decod2a4

todas '0'

misma

secuencia

Figura 5.2: Tabla de verdad del decodificador de 3 a 8 dividida según el valor de E y A2

Por tanto, podemos usar dos decodificadores de 2 a 4, uno para las señales S3 a S0, que se activará cuando

E=1 y A2=0 ; esto es E·A2 ⎯⎯

; y otro decodificador para las señales S7 a S4, que se activará cuando E=1 y A2=1(E·A2). La salida S0 de este último decodificador de 2 a 4 irá a la salida S4 del decodificador de 3 a 8, y asísucesivamente con el resto de señales.

5/10/2018 pract_xilinx92 - slidepdf.com

http://slidepdf.com/reader/full/practxilinx92 29/94

Departamento de Tecnología Electrónica 5. Decodificador de 3 a 8

Diseño digital con esquemáticos y FPGA. v1.8 - 04/06/2008 28