Sobre DSCH 2 y Microwind 2

-

Upload

ricardo-parra -

Category

Documents

-

view

71 -

download

0

Transcript of Sobre DSCH 2 y Microwind 2

Diseño CMOS con Dsch y Microwind

1

DSCH 2 Esta aplicación consta de un editor lógico, basado en captura de esquemas, y un simulador. Está orientado a la validación del circuito lógico antes de pasar a la fase de síntesis microelectrónica. Proporciona un entorno sencillo para el diseño lógico jerárquico y simulación con análisis de retardos, todo lo cual permite el diseño y validación de estructuras lógicas complejas. Una característica muy interesante es la posibilidad de estimar el consumo de potencia del circuito. Además, es capaz de generar un fichero Verilog del circuito lógico que puede tomar como entrada la aplicación Microwind 2 para crear el layout. Descripción del entorno El entorno gráfico de Dsch 2 es muy sencillo. Consta de una barra de menú, una barra de herramientas con las tareas más comunes y la superficie de edición. Al arrancar la aplicación aparece una ventana flotante con la librería de símbolos.

Captura de esquemas La captura de esquemas se realiza arrastrando los símbolos que aparecen en la ventana flotante a la superficie de edición. La definición de los símbolos se encuentra en ficheros de extensión .sym (en la carpeta IEEE). Además de los símbolos establecidos por la normalización, es posible insertar símbolos creados por el usuario (Insert ���� User Symbol (.SYM)) o esquemas salvados previamente (Insert ���� Another Schema (.SCH)). De esta manera se facilita el diseño jerárquico, utilizando modelos de circutios previos en los nuevos. Para crear un símbolo de usuario utilizamos File ���� Schema to new symbol que salva en un fichero .sym el esquema completo del circuito actual. El esquema se puede salvar en un fichero con extensión .sch.

Diseño CMOS con Dsch y Microwind

2

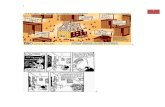

Simulación La simulación se realiza sobre el propio esquema mediante Simulate ���� Start simulation. Los dispositivos virtuales de entrada y salida (teclado hexadecimal, diodo led y display de 7 segmentos) facilitan la entrada de datos y la visualización de resultados. La figura siguiente ilustra un instante de la simulación con 2 teclados hexadecimales con los valores 4 y 5 respectivamente y el display de 7 segmentos indicando el resultado de la suma (9 en este caso). Los dispositivos virtuales de E/S no forman parte del esquema. Junto al esquema aparece una ventana flotante para el control de la simulación en curso.

Salida para Microwind 2 El proceso es el siguiente:

1. Crear el fichero Verilog: File ���� Make Verilog File. Podemos cambiar el nombre del fichero asignado por defecto. El fichero Verilog tiene extensión .txt.

2. Abrir Microwind 2 y compilar el fichero Verilog creado anteriormente: Compile ���� Compile Verilog File. En la ventana de diálogo pulsar Compile.

Diseño CMOS con Dsch y Microwind

3

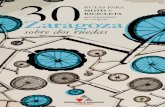

MICROWIND 2 Esta aplicación nos permite diseñar y simular circuitos integrados al más bajo nivel, a nivel microelectrónico. Consta de librerías de componentes ya diseñados que nos pueden ayudar a introducirnos el mundo del diseño digital CMOS. Como ejemplo se adjunta una figura con un esquema de un inversor: Descripción del entorno El entorno de Microwind 2 es sencillo. Consta de una barra de menú, una barra de herramientas y la superficie de edición. Cuando arranca la aplicación aparece una ventana flotante con la paleta de edición. Dicha paleta de edición nos permite implantar en silicio transistores CMOS, resistencias, inductancias, cables, etc.

Cualquier diseño puede salvarse en un fichero con extensión .MSK. La aplicación consta, como ya se ha indicado, con librerías de circuitos integrados ya realizados. Se han diseñado manualmente con lo que se asegura que ocupan la menor superficie de silicio posible, es decir, son diseños óptimos. Otra manera de generar circuitos integrados es mediante la compilación de modelos descritos con Verilog. Esta compilación genera automáticamente un layout (circuito integrado en silicio) conforme a una serie de reglas contenidas en el fichero default.rul. Este diseño no tiene por

Diseño CMOS con Dsch y Microwind

4

que ser el de área mínima ya que no ha sido optimizado. Seguidamente vemos un ejemplo de layout generado por compilación.

Simulación Los circuitos diseñados (o compilados) pueden ser simulados mediante el comando Simulate ���� Run simulation…. La simulación genera las curvas de evolución en tensiones y corrientes. También puede realizarse la simulación sobre el propio layout. Proceso de implantación microelectrónica También es posible reproducir el proceso de implantación en silicio con la secuencia pasos de fotolitografía. Accedemos a esto en Simulate ���� Process steps in 3D.