Unidad I Programación VHDLsagitario.itmorelia.edu.mx/actelleza/DDV/U1-8.pdf · Ejemplo (Sumador 4...

Transcript of Unidad I Programación VHDLsagitario.itmorelia.edu.mx/actelleza/DDV/U1-8.pdf · Ejemplo (Sumador 4...

UNIDAD IPROGRAMACIÓN VHDLInstanciación

Dra. Adriana del Carmen Téllez Anguiano

INSTANCIACIÓN

o Se diseña un circuito en un archivo VHDL, una vezverificado su correcto funcionamiento, se puedeutilizar como un componente en otros diseños(archivos VHDL de mayor jerarquía).

o Algunos diseños son vendidos como IP (IntellectualProperty) para que terceras personas lo utilicen.

o Se entrega la versión sintetizada, no el códigofuente

Dra. Adriana del Carmen Téllez Anguiano

INSTANCIACIÓN

o Para utilizar el diseño o IP deseados, se debe declarar

como componente en el archivo VHDL de jerarquía

mayor.

o Se instancia (coloca) después del begin de la

arquitectura, indicándole qué se conecta a sus

entradas y salidas (port map).

o Equivale a colocar al circuito en el impreso o protoboard

y poner los alambres de conexión.

Dra. Adriana del Carmen Téllez Anguiano

INSTANCIACIÓNEjemplo (Sumador 4 bits seudoparalelo)

Se utiliza el diseño de un sumador completo de 1 bit

(FA – Full Adder)

a b cin

FA

cout s

a b cin

cout s

a b cin cout s

0 0 0 0 0

0 0 1 0 1

0 1 0 0 1

0 1 1 1 0

1 0 0 0 1

1 0 1 1 0

1 1 0 1 0

1 1 1 1 1

cout <= (a and cin) or (b and cin) or (a and b);

s <= a xor b xor cin;

Dra. Adriana del Carmen Téllez Anguiano

INSTANCIACIÓNEjemplo (Sumador 4 bits seudoparalelo)

a b cin

FA

cout s

a0 b0

c0 s0

a b cin

FA

cout s

a1 b1 c0

c1 s1

a b cin

FA

cout s

a2 b2 c1

c2 s2

a b cin

FA

cout s

a3 b3 c2

c3 s3

Dra. Adriana del Carmen Téllez Anguiano

INSTANCIACIÓNEjemplo (Sumador 4 bits seudoparalelo)

Se programa el sumador completo de 1 bit library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity sumc is

Port ( a : in STD_LOGIC;

b : in STD_LOGIC;

cin : in STD_LOGIC;

cout : out STD_LOGIC;

s : out STD_LOGIC);

end sumc;

architecture Behavioral of sumc is

begin

cout <= (a and b) or (b and cin) or (a and cin);

s <= a xor b xor cin;

end Behavioral;

Dra. Adriana del Carmen Téllez Anguiano

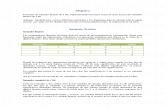

INSTANCIACIÓNEjemplo (Sumador 4 bits seudoparalelo)

Se verifica su funcionamiento en simulación

stim_proc: process

begin

a <= '0'; b <= '0'; cin <='0'; wait for 10 ns;

a <= '0'; b <= '0'; cin <='1'; wait for 10 ns;

a <= '0'; b <= '1'; cin <='0'; wait for 10 ns;

a <= '0'; b <= '1'; cin <='1'; wait for 10 ns;

a <= '1'; b <= '0'; cin <='0'; wait for 10 ns;

a <= '1'; b <= '0'; cin <='1'; wait for 10 ns;

a <= '1'; b <= '1'; cin <='0'; wait for 10 ns;

a <= '1'; b <= '1'; cin <='1'; wait for 10 ns;

wait;

end process;

Dra. Adriana del Carmen Téllez Anguiano

INSTANCIACIÓNEjemplo (Sumador 4 bits seudoparalelo)

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity sum4b is

Port ( A : in STD_LOGIC_VECTOR (3 downto 0);

B : in STD_LOGIC_VECTOR (3 downto 0);

Cin : in STD_LOGIC;

Cout : out STD_LOGIC;

S : out STD_LOGIC_VECTOR (3 downto 0));

end sum4b;

architecture Behavioral of sum4b is

component sumc

Port ( a : in STD_LOGIC;

b : in STD_LOGIC;

cin : in STD_LOGIC;

cout : out STD_LOGIC;

s : out STD_LOGIC);

end component;

Dra. Adriana del Carmen Téllez Anguiano

INSTANCIACIÓNEjemplo (Sumador 4 bits seudoparalelo)

signal C : std_logic_vector(2 downto 0);

begin

Inst_SC0: sumc PORT MAP(

a => A(0),

b => B(0),

cin => Cin,

cout => C(0),

s => S(0));

Inst_SC1: sumc PORT MAP(

a => A(1),

b => B(1),

cin => C(0),

cout => C(1),

s => S(1));

Dra. Adriana del Carmen Téllez Anguiano

INSTANCIACIÓNEjemplo (Sumador 4 bits seudoparalelo)

Inst_SC2: sumc PORT MAP(

a => A(2),

b => B(2),

cin => C(1),

cout => C(2),

s => S(2));

Inst_SC3: sumc PORT MAP(

a => A(3),

b => B(3),

cin => C(2),

cout => Cout,

s => S(3));

end Behavioral;

Dra. Adriana del Carmen Téllez Anguiano

INSTANCIACIÓNEjemplo (Sumador 4 bits seudoparalelo)

Se verifica su funcionamiento en simulaciónUSE ieee.numeric_std.ALL; (Agregar)

stim_proc: process

begin

for i in std_logic range '0' to '1' loop

Cin <=i;

for j in 0 to 15 loop

A <= std_logic_vector(to_unsigned(j,4));

for k in 0 to 15 loop

B <= std_logic_vector(to_unsigned(k,4));

wait for 10 ns;

end loop;

end loop;

end loop;

end process;

Dra. Adriana del Carmen Téllez Anguiano

INSTANCIACIÓN

Uso de múltiples arquitecturas

o Una entidad puede tener múltiples arquitecturas,

dependiendo qué se desea optimizar.

o Al utilizar esa entidad como componente en código

VHDL de mayor jerarquía, se debe indicar qué

arquitectura se utiliza en cada instanciación.

o Esto se hace por medio de la configuración de la

componente.

Dra. Adriana del Carmen Téllez Anguiano

INSTANCIACIÓN

Uso de múltiples arquitecturas

architecture Behavioral of SUMADOR8BCD is-------- Declaración del componenteCOMPONENT sumador8b is

Port ( A : in STD_LOGIC_VECTOR (7 downto 0);B : in STD_LOGIC_VECTOR (7 downto 0);S : out STD_LOGIC_VECTOR (7 downto 0);co : out STD_LOGIC);

end COMPONENT;

-------- Configuración del componentefor U1: sumador8b use entity work.sumador8b(NombreArquitectura);signal CCLK: std_logic:='0';

Begin-------- Instanciación del componenteU1: sumador8b port map (A,B,S,CO);

Dra. Adriana del Carmen Téllez Anguiano

ALIAS

• En ocasiones se requiere llamar una señal condiferente nombre en diferentes partes del código.

• En otras se requiere llamar una parte de un vectorde una manera y el resto de otra.

• Esto se puede hacer usando la definición de alias.

Dra. Adriana del Carmen Téllez Anguiano

ALIAS

Ejemplos

• signal ABC: std_logic_vector(2 downto 0);

• alias AA is ABC(2);

• alias BB is ABC(1);

• alias CC is ABC(0);

• signal Real: std_logic_vector(31 downto 0);

• alias mantisa is Real(23 downto 0);

• alias exponente is Real(30 downto 24);

• alias signo is Real(31);

Dra. Adriana del Carmen Téllez Anguiano

DISEÑOS GENÉRICOS

o En ocasiones se necesita:

o Utilizar el mismo diseño con señales o variables de diferente tamaño.

oCircuitos con varias secciones iguales o repetidas.

o Ejemplo:

Sumador con Acarreo en Cascada

o Resulta incómodo modificar el diseño para ajustarlo al tamaño deseado o repetir código múltiples veces.

Dra. Adriana del Carmen Téllez Anguiano

DISEÑOS GENÉRICOS

o Para estas situaciones la solución es tener diseñosgenéricos:

o Se añade(n) un(os) parámetro(s) adicional(es)para definir el tamaño o el número derepeticiones.

o Se añaden declaraciones en función de estenuevo parámetro.

Dra. Adriana del Carmen Téllez Anguiano

DISEÑOS GENÉRICOS

o En la entidad se definen los parámetros genéricos.

o En función del parámetro genérico, se puede indicar

el tamaño de:

o Los puertos

o Las variables

o Las señales internas

• entity SumadorNbits is

• generic (i: natural);

• port(A,B : in std_logic_vector (i-1 downto 0);

• S : out std_logic_vector (i-1 downto 0);

• co : out std_logic);

• ...

• signal C : std_logic_vector (i-1 downto 0);

• …

Dra. Adriana del Carmen Téllez Anguiano

DISEÑOS GENÉRICOS

o En la arquitectura se pueden “generar” (repetir)

bloques, el número de veces que indique el

parámetro genérico, con solo una línea de código:

genera: for j in 0 to i-2 generate

begin

U:sumadorc port map (a(j+1), b(j+1), s(j+1), c(j),c(j+1));

end generate;

Dra. Adriana del Carmen Téllez Anguiano

DISEÑOS GENÉRICOS

o Los diseños genéricos por si solos:

oNo son sintetizables (no se pueden implementar

en un circuito).

o Para poder implementar en hardware un diseño

genérico:

o Se debe tener otro archivo VHD de mayor

jerarquía que instancie el diseño genérico, dando

valor al parámetro genérico.

Dra. Adriana del Carmen Téllez Anguiano

DISEÑOS GENÉRICOS

o Al instanciar, se define el valor del parámetro genérico

y por tanto se define el tamaño real de los puertos y

del diseño:

component SumadorNbits

generic (i: natural);

port(A,B,Ci: in std_logic_vector(i-1 downto 0);

S,Co: out std_logic_vector(i-1 downto 0));

end component ;

…

U3:SumadorNbits generic map (7) port map (A,B,Ci,S,Co);

…

Dra. Adriana del Carmen Téllez Anguiano