ADC12

description

Transcript of ADC12

Introducción 1 ADC12

Seminario de Computadores I

¿Que Hace?

•Convierte valores de voltaje a palabras digitales.

Características

• Conversión de 12 bits.

• Tasa de muestreo programable, con una máxima: 200 KHz.

• Inicio de la conversión por software, o por temporizadores .

• Término de la conversión genera interrupciones.

• Generación de referencias configurable por software.

• 8 canales de entrada, ademas de 4 señales internas.

• 4 modos de adquisión.

• 16 registros de almacenamiento del resultado de la conversión.

Introducción 4 ADC12

Seminario de Computadores I

Qué entrega el conversor:

Convierte en palabras de 12 bits los voltajes aplicados en sus canales, dentro de los rangos V+ y V-.

La conversión cumple la siguiente relación:

Obteniendose en memoria la representación binaria del número resultante.

Introducción 5 ADC12

Seminario de Computadores I

Requerimientos para la operación:

Reloj (ADC12CLK)

Fuentes:

• SMCLK

• MCLK

• ACLK

• ADC12OSC

Con ADC12DIVx se puede dividir en un factor 1 a 8.

Introducción 6 ADC12

Seminario de Computadores I

Canales

•En un multiplexor se elige el canal que sera muestreado y convertido.

• Se pueden (y deben) seleccionar mediante software.

•Corresponden al P6.

Introducción 7 ADC12

Seminario de Computadores I

Voltajes de referencia

• Referencia interna: 2.5 o 1.5 [V].

• Referencia externa, tanto para V_ como V+.

• Voltaje de polarización: 3.6 [V].

Introducción 8 ADC12

Seminario de Computadores I

Muestreo y tiempos de conversión

El ciclo de conversión se inicia con un canto de subida de SHI.

Fuentes de esta señal:

• Bit ADC12SC.

• Etapa de salida 1 del Timer_A.

• Etapa de salida 0 del Timer_B.

• Etapa de salida 1 del Timer_B.

La señal SAMPCON controla el período de muestreo y el inicio de la conversión.

Existen dos modos de muestreo, que se setean con el bit SHP.

Introducción 9 ADC12

Seminario de Computadores I

Captura extendida

En este modo, la señal SHI controla directamente a SAMPCON y define la longitud del período de muestreo.

Introducción 10 ADC12

Seminario de Computadores I

Captura por pulso

La señal SHI es utilizada en este caso para disparar el temporizador de muestreo.

Bits SHTxx de ADC12CTL0 definen período de SAMPCON.

El tiempo total de muestreo es entonces tsample + tsync.

Introducción 11 ADC12

Seminario de Computadores I

Consideraciones del tiempo de captura

El canal se puede modelar como un circuito RC pasabajos:

Debe considerarse entonces como tiempo de muestreo:

Reemplazando valores típicos, se obtiene un tsample mínimo de 4,33 [us] .

Registros 1 ADC12

Seminario de Computadores I

Caracteristicas:

• 2 registros de configuración

• 16 registros de almacenamiento

• 3 registros para manejo de interrupciones.

•16 registros de control de conversión

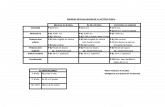

Registros 2 ADC12

Seminario de Computadores I

ADC 12 Control Register 0

ADC12CTL0

SHT1x: Nº de ciclos en el periodo de muestreo para los registros desde ADC12MEM8 al ADC12MEM15

SHT0x: Nº de ciclos en el periodo de muestreo para los registros desde ADC12MEM0 al ADC12MEM7

MSC: Muestreo y conversion multiples

0 = se necesita canto positivo de SHI para cada muestreo

1 = se necesita canto positivo de SHI para primer muestreo

Registros 3 ADC12

Seminario de Computadores I

ADC 12 Control Register 0

ADC12CTL0

REF2_5V: Generador de voltaje referencia . 0 = 1,5[V] 1 = 2,5[V]

REFON: Activa el generador de referencia

ADC12ON: Habilita el ADC

ADC12OVIE: Habilita la interrupción debido al Overflow en resultados

ADC12TOVIE: Habilita la interrupción por TimeOverflow en la conversión

ENC: Habilita la conversión

ADC12SC: Inicia la conversión

Registros 4 ADC12

Seminario de Computadores I

ADC 12 Control Register 1

ADC12CTL1

CSTARTADDx: Indica en que registro de memoria (ADC12MEMx) iniciar la conversión

SHSx: Fuente de reloj que inicia todo el ciclo de conversion

ISSH: Invertir la señal Sample&Hold

Registros 5 ADC12

Seminario de Computadores I

ADC 12 Control Register 1

ADC12CTL1

SHP: Configura el modo del pulso del Sample&Hold. Configura el trigger de la señal de muestreo SAMPCON

0 captura extendida

1 captura por pulso

ADC12SSELx: Origen del reloj ADC12CLK

ADC12DIVx: Dividir el reloj ADC12CLK

Registros 6 ADC12

Seminario de Computadores I

ADC 12 Control Register 1

ADC12CTL1

CONSEQx: Modo de Conversión

ADC12BUSY: Indica si el ADC esta ocupado realizando alguna operación

00 = 1 conversión, 1 canal01 = Secuencia de canales10 = Repetir un único canal11 = Repetir secuencia de canales

Registros 7 ADC12

Seminario de Computadores I

ADC 12 Conversion Memory Register,

ADC12MEMx

Se almacenan los resutaldos de la conversión.

Se emplean solo los bits 11 al 0

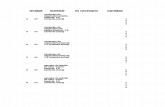

Registros 8 ADC12

Seminario de Computadores I

ADC 12 Conversion Memory Control Register,

ADC12MCTLx

EOS: Fin de la secuencia

SREFx: Seleccionar la referencia

INCHx: Seleccionar el canal de entrada

Registros 9 ADC12

Seminario de Computadores I

ADC 12 Interrupt Enable Register,

ADC12IEHabilita la petición de

interrupciones por parte de

ADC12IFGx.

ADC 12 Interrupt Flag Register,

ADC12IFGADC12IFGx: Se ponen en 1 cuando al registro ADC12MEMx se le guarda una conversión

Registros 10 ADC12

Seminario de Computadores I

ADC 12 Interrupt Vector Register,

ADC12IV

ADC12IVx: Almacena el valor del vector de

interrupciones

Funcionamiento 1 ADC12 Memoria de conversión

Seminario de Computadores I

- Existen 16 registros de memoria denominados ADC12MEMx.- Cada registro de memoria es asociado a los registros de control ADC12MCTLx.

- SREF indica la referencia a usar.

- INCHx selecciona el canal a convertir.

- EOS indica el termino de una secuencia, en el caso que se - ocupe una.- CSTARTADDx define el primer ADC12MEMx a ocupar en una secuencia.- Cuando un resultado es guardado en un ADC12MEMx, el correspondiente flag es seteado en el registro ADC12IFG.

Funcionamiento 2 ADC12 Modos de Conversión

Seminario de Computadores I

Los modos de conversión son seteados mediante CONSEQx.

00 Canal único, única conversión

01 Secuencia de canales

10 Repetición de canal único

11 Repetición Secuencia de canales

CONSEQx

Funcionamiento 3 ADC12

Seminario de Computadores I

ADC12off X=CSTARTADDx

Resultado guardadoen ADC12MEMx,

ADC12IFGx es seteado

Canal definido en

ADC12MCTLx

Conversión

ENC = 1SHSx = 0ADC12SC =

12 x ADC12CLK

1 x ADC12CLKSAMPCOM =

ADC12ON

Canal único, única conversión

Funcionamiento 3 ADC12

Seminario de Computadores I

ADC12off X=CSTARTADDx

Resultado guardadoen ADC12MEMx,

ADC12IFGx es seteado

Canal definido en

ADC12MCTLx

Conversión

ENC = 1SHSx = 0ADC12SC =

12 x ADC12CLK

1 x ADC12CLKSAMPCOM =

ADC12ON

Canal único, única conversión

Wait trigger

ENC

SAMPCOM =

Funcionamiento 4 ADC12

Seminario de Computadores I

ADC12off X=CSTARTADDx

Resultado guardadoen ADC12MEMx,

ADC12IFGx es seteado

Canal definido en

ADC12MCTLx

Conversión

ENC = 1SHSx = 0

ADC12SC =

12 x ADC12CLK

1 x ADC12CLK

MSC = 1SHP = 1EOS.x = 0If x<15 then x = x+1Else x = 0

EOS.x = 1

SAMPCOM =

ADC12ON

Secuencia de canales

Funcionamiento 4 ADC12

Seminario de Computadores I

ADC12off X=CSTARTADDx

Resultado guardadoen ADC12MEMx,

ADC12IFGx es seteado

Canal definido en

ADC12MCTLx

Conversión

ENC = 1SHSx = 0

ADC12SC =

12 x ADC12CLK

1 x ADC12CLK

MSC = 1SHP = 1EOS.x = 0If x<15 then x = x+1Else x = 0

EOS.x = 1

SAMPCOM =

ADC12ON

Secuencia de canales

Wait trigger

ENC

SAMPCOM =

MSC = 0O SHP = 0

Y EOS.x = 0If x<15 then x = x+1

Else x = 0

Funcionamiento 5 ADC12

Seminario de Computadores I

ADC12off X=CSTARTADDx

Resultado guardadoen ADC12MEMx,

ADC12IFGx es seteado

Canal definido en

ADC12MCTLx

Conversión

12 x ADC12CLK

1 x ADC12CLK

ADC12off X=CSTARTADDx

Resultado guardadoen ADC12MEMx,

ADC12IFGx es seteado

Canal definido en

ADC12MCTLx

Conversión

ENC = 1SHSx = 0

ADC12SC =

12 x ADC12CLK

1 x ADC12CLK

MSC = 1SHP = 1ENC = 1

ENC = 0

SAMPCOM =

ADC12ON

Repetición de canal único

Funcionamiento 5 ADC12

Seminario de Computadores I

ADC12off X=CSTARTADDx

Resultado guardadoen ADC12MEMx,

ADC12IFGx es seteado

Canal definido en

ADC12MCTLx

Conversión

12 x ADC12CLK

1 x ADC12CLK

ADC12off X=CSTARTADDx

Resultado guardadoen ADC12MEMx,

ADC12IFGx es seteado

Canal definido en

ADC12MCTLx

Conversión

ENC = 1SHSx = 0

ADC12SC =

12 x ADC12CLK

1 x ADC12CLK

MSC = 1SHP = 1ENC = 1

ENC = 0

SAMPCOM =

ADC12ON

Repetición de canal único

Wait trigger

ENC

SAMPCOM =

MSC = 0O SHP = 0Y ENC = 1

Funcionamiento 6 ADC12

Seminario de Computadores I

ADC12off X=CSTARTADDx

Resultado guardadoen ADC12MEMx,

ADC12IFGx es seteado

Canal definido en

ADC12MCTLx

Conversión

1 x ADC12CLK

Resultado guardadoen ADC12MEMx,

ADC12IFGx es seteado

Canal definido en

ADC12MCTLx

Conversión

ENC = 1SHSx = 0

ADC12SC =

12 x ADC12CLK1 x ADC12CLK

MSC = 1SHP = 1ENC = 1 o EOS.x = 0

If EOS.x = 1 then x = CSTARTADDxElse {If x<15 then x = x+1Else x = 0}

EOS.x = 1ENC = 0

SAMPCOM =

ADC12ON

Repetición Secuencia de canales

Funcionamiento 6 ADC12

Seminario de Computadores I

ADC12off X=CSTARTADDx

Resultado guardadoen ADC12MEMx,

ADC12IFGx es seteado

Canal definido en

ADC12MCTLx

Conversión

1 x ADC12CLK

Resultado guardadoen ADC12MEMx,

ADC12IFGx es seteado

Canal definido en

ADC12MCTLx

Conversión

ENC = 1SHSx = 0

ADC12SC =

12 x ADC12CLK1 x ADC12CLK

MSC = 1SHP = 1ENC = 1 o EOS.x = 0

If EOS.x = 1 then x = CSTARTADDxElse {If x<15 then x = x+1Else x = 0}

EOS.x = 1ENC = 0

SAMPCOM =

ADC12ON

Repetición Secuencia de canales

Wait trigger

ENC

SAMPCOM =

MSC = 1SHP = 1

ENC = 1 o EOS.x = 0

If EOS.x = 1 then x = CSTARTADDx

Else {If x<15 then x = x+1Else x = 0}

Funcionamiento 7 ADC12

Seminario de Computadores I

- (00) Para interrumpir la conversión, se debe resetear el bit ENC haría terminar inmediatamente la conversión, lo que implicaría que el resultado de la conversión no seria confiable.- (01) Para interrumpir la conversión se debe resetear el bit ENC terminaría la conversión al final de la secuencia.- (10) Para interrumpir la conversión se debe resetear el bit ENC terminaría la conversión al final de ésta.- (11) Las sucesivas conversiones terminan cuando ENC es igual a 0 y EOS = 1, lo que hace terminar la conversión al final de la secuencia.

Interrupción de la conversión

Funcionamiento 8 ADC12 Sensor integrado de temperatura

Seminario de Computadores I

- Se debe seleccionar la entrada analoga INCHx=1010.- La temperatura se encuentra relacionada con el voltaje de entrada

mediante el siguiente grafico.

0,8

0,9

1

1,1

1,2

1,3

-100 -50 0 50 100

Temperatura

Vo

ltaje

Vtemp = 0.00355Tempc+0.986

Funcionamiento 9 ADC12 Interrupciones

Seminario de Computadores I

- El ADC12 posee 18 recursos de interrupción.

* ADC12IFG0-ADC12IFG15

* ADC12OV, ADC12MEMx overflow

* ADC12TOV, ADC12 conversion time overflow

Funcionamiento 10 ADC12

ADC12IV, Vector generador de interrupción

Seminario de Computadores I

-Vector único de interrupciones.-En éste las interrupciones son priorizadas y combinadas.-Las interrupciones ADC12TOV y ADC12OV son reseteadas automáticamente con cualquier acceso a este registro, en el caso que tenga cualquiera de estas la mayor prioridad.

-Las interrupciones originadas por ADC12IFGx son seteadas una vez que se hayan leido los datos de los registros de memoria ADC12MEMx

correspondiente. -Si otra interrupción queda pendiente después del servicio de interrupción otra interrupción es generada.

Programación 1 ADC12

Seminario de Computadores I

void ADC_INIT_SIMPLE(void) {P6SEL |= 0x00FF; //8 lsb Puerto 6 para conversor ADC12P6DIR &= 0xFF00; //8 lsb Puerto 6 como entradas (analogas)ADC12CTL0 &= ~ENC; //deshabilita conversion

ADC12CTL0 = SHT1_15 | SHT0_15 | ADC12ON;

ADC12CTL1 = CSTARTADD_0 | SHS_0 | SHP | ADC12DIV_7 | ADC12SSEL_2 | CONSEQ_0;

ADC12MCTL0 = SREF_0;

ADC12IE = 0x00; //Deshabilitadas las interrupciones (bits ADC12IEx) para todos los ADC12MCTLx

ADC12CTL0 |= ENC; // habilita conversión}

Inicialización Secuencial

ADC12CTL0 = SHT1_15 | SHT0_15 | ADC12ON;//SHT1x = 0x0F => Tiempo de Sample and Hold para canales ADC 8 a

15 = 1024 ciclos ADC12CLK//SHT0x = 0x0F => Tiempo de Sample and Hold para canales ADC 0 a

7 = 1024 ciclos ADC12CLK

//MSC no importa, sólo válido para conversiones múltiples o repetitivas

//REF2_5V no importa si REFON = 0//REFON = 0, referencia interna apagada//ADC12ON = 1 => Conversor ADC12 encendido//ADC12OVIE = 0 => NO se utiliza Interrupcion de overflow de

memoria del ADC12//ADC12TOVIE deshabilitado//ENC = 0 => Conversion Deshabilitada, para poder modificar el

siguiente registro//ADC12SC = 0 => No se inicia conversión

Programación 2 ADC12 DetalleInicializaciónSimple

ADC12CTL1 = CSTARTADD_0 | SHS_0 | SHP | ADC12DIV_7 | ADC12SSEL_2 | CONSEQ_0;

//CSTARTADDx = 0 => Conversión dado por los argumentos del registro ADC12MCTL0 y por lo tanto resultado aparece en ADC12MEM0

//SHSx = 0 => Sample and Hold Source = ADC12SC bit//SHP = 1 => Canto de bajada del SHI "NO" detiene el ciclo de

"Captura" de la señal de entrada.//ISSH = 0 => Polaridad normal del SHI

//ADC12DIVx = 7 => ADC12 clock divider = /8 => ADC12 clock = 1MHz//ADC12SSELx = 2 => ADC12 Clock = MCLK//CONSEQx = 0 => MODO DEL ADC12: Una única conversión, un único

canal

Programación 3 ADC12 DetalleInicializaciónSimple

ADC12MCTL0 = SREF_0;

//EOS no importa, Indica la última conversión en una secuencia cuando modo ADC12 = cíclico o secuencia.

//SREF_x = 0 => Referencia de voltaje VR+ = AVcc y VR- = AVss, es decir, VR+ = 3.6[V] y VR- = 0[V]

//INCHx = 0 => Parte con canal 0 seleccionado como entrada al ADC12

ADC12IE = 0x00; //Deshabilitadas las interrupciones (bits ADC12IEx) para todos los ADC12MCTLx

ADC12CTL0 |= ENC; // habilita conversión

}

Programación 4 ADC12 DetalleInicializaciónSimple

Programación 5 ADC12

Seminario de Computadores I

Conversión Simple

int conversion(CANAL) {

ADC12CTL0 &= ~ENC; //deshabilita conversion para realizar cambios

ADC12MCTL0 &= 0xFFF0; //borra INCHx

ADC12MCTL0 |= (CANAL & 0x0F); //Selecciona el canal a convertir

ADC12CTL0 |= ENC; //habilita conversión

ADC12CTL0 |= ADC12SC; //inicia conversión

while (ADC12CTL0 & ADC12SC); //espera término de la conversión, o sea espera que bit ADC12SC = 0

return ADC12MEM0;

}

Inicialización Secuencial

void ADC_INIT_SEQ(void){

P6SEL |= 0x00FF;P6DIR &= 0xFF00;

ADC12CTL0 &= ~ENC; //Para poder hacer cambios en los registros

ADC12CTL0 = SHT1_15 | SHT0_15 | ADC12ON | MSC;//MSC =1 => Cada conversión se realiza apenas la anterior haya

terminado

ADC12CTL1 = CSTARTADD_0 | SHS_0 | SHP | ADC12DIV_7 | ADC12SSEL_2 | CONSEQ_1;

//CONSEQx = 1 => MODO DEL ADC12: Secuencia de canales.

ADC12MCTL0 = SREF_0;ADC12MCTL1 = SREF_0;ADC12MCTL2 = SREF_0;ADC12MCTL3 = SREF_0 | EOS;// último canal de la secuenciaADC12IE = 0x00;ADC12CTL0 |= ENC; // habilita conversión}

Programación 6 ADC12

Conversión Secuencialvoid CONV_ADC_SEQ(int CH1,CH2,CH3,CH4){ADC12CTL0 &= ~ENC; ADC12MCTL0 &= 0xFFF0;ADC12MCTL1 &= 0xFFF0;ADC12MCTL2 &= 0xFFF0;ADC12MCTL3 &= 0xFFF0;ADC12MCTL0 |= (CH1 & 0x0F);//Selecciona 1º canal a convertirADC12MCTL1 |= (CH2 & 0x0F);//Selecciona 2º canalADC12MCTL2 |= (CD3 & 0x0F);//Selecciona 3º canalADC12MCTL3 |= (CH4 & 0x0F);//Selecciona 4º canalADC12CTL0 |= ENC;ADC12CTL0 |= ADC12SC;while (ADC12CTL0 & ADC12SC);

ResultadoADC[0]=ADC12MEM0; //Los resultados de la conversiónResultadoADC[1]=ADC12MEM1; //se almacenan en variables globalesResultadoADC[2]=ADC12MEM2;ResultadoADC[3]=ADC12MEM3;}

Programación 7 ADC12