Arquitectura_FPGA

-

Upload

ferdinandja -

Category

Documents

-

view

226 -

download

0

Transcript of Arquitectura_FPGA

-

8/6/2019 Arquitectura_FPGA

1/12

1.1. Tecnologas de diseo de circuitos integradosDurante la dcada de los 80, varias compaas intentaron resolver el viejo

compromiso de complejidad versus estandarizacin. Por un lado se tena la opcin barata

del microprocesador, componente completamente estndar, y por otro lado los ASICSdenominados full-custom, es decir, circuitos integrados de aplicacin especfica diseadoscompletamente a medida, ptimos pero muy caros. En estos, los ingenieros diseabantodas las mscaras presentes en el proceso de fabricacin de los circuitos integrados.

Tambin exista la posibilidad de realizar diseos denominados semi-custom, con lastecnologas denominadas Gate Array y Standard Cells [3]. En la tecnologa Gate Arrays seestandarizan las etapas iniciales de fabricacin, por lo que los clientes comparten unaestructura similar en forma de filas de transistores sin interconexin. La conexin serealizaba a medida en las ltimas fases del proceso de fabricacin, diseando a media una oms capas de metalizaciones, finalizando as el diseo. La tecnologa Standard Cells, en

cambio, no era un proceso premanufacturado, pero se dispone de clulas prediseadas yestandarizadas, como RAMs, ALUs, multiplicadores, etctera, con lo que se optimiza endensidad, velocidad y rea respecto los Gate Arrays.

Una de las maneras de caracterizar las prestaciones de un diseo digital es evaluarconjuntamente el rea que ocupa, la velocidad mxima a la que puede operar y la potenciaque consume, lo que se denomina figura ATP (rea-tiempo-potencia). Teniendo esto encuenta, los ASICs tienen mejores prestaciones que los componentes estndares tipomicroprocesador, adems de ser ms confidenciales y fiables. Por el contrario, los ASICsson mucho ms difciles de depurar y tienen un coste fijo elevado, por lo que requieren un

volumen de fabricacin muy elevado. Pero lo peor era, sin duda, la imposibilidad decorregir errores, ya que una vez se enviaba el circuito a fabricar, era imposible hacer

modificaciones.

Los avances en la tecnologa hacan que se pudieran elaborar sistemas cada vez mscomplejos, lo que hace inevitable la aparicin de errores. Adems, la propia complejidad delos sistemas haca que su diseo supusiera cada vez un tiempo mayor. Por otra parte, la leyde Moore haca obsoleto cualquier producto en dos aos, que se vea reflejado en unapresin adicional sobre los diseadores.

1.2. Dispositivos lgicos programablesLa crisis anteriormente citada hizo que algunos ingenieros buscaran ofrecer un

producto, o una metodologa de diseo que combinara el notable ATP de los ASICs conlas ventajas centrales de los microprocesadores: bajo costo, alta estandarizacin, facilidadde correccin de errores y reduccin del tiempo de salida al mercado.

Varias compaas se lanzaron en los 80 a fabricar un ASIC reprogramable. La idea erasencilla: en primer lugar, reemplazar la interconexin fija de los Gate ArraysyStandard Cellspor una serie de pistas metlicas conectables por transistores de paso controlados por unconjunto de bits de control almacenados en una memoria interna.

Histricamente, los arreglos de lgica programable (PLA) fueron los primerosdispositivos lgicos programables. Los PLA contenan compuertas AND y OR con unaestructura de dos niveles (figura 1.4), con conexiones programables por el usuario [4]. La

estructura de los PLA sufri mejoras y su costo disminuy con la introduccin dedispositivos lgicos de arreglo programable (PAL), en los que el arrayde puertas OR es fijo

-

8/6/2019 Arquitectura_FPGA

2/12

(no programable) y los dispositivos de arreglos genricos (GAL). Actualmente, talesdispositivos se denominan de manera genrica como dispositivos de lgica programable yse puede decir que son los MSI de la industria de la lgica programable.

Figura 1.4a. PLA 4x6x3, arrays de puertas AND y ORprogramables. Figura 1.4b. PAL 4x6x3, array de puertas ORfija

Estos dispositivos, antecesores de las FPGAs, ya se configuraban haciendo uso de unlenguaje de descripcin de hardware, en los que se profundizar ms adelante. Sin embargo,la configuracin de los primeros circuitos se realizaba, inicialmente, mediante ladestruccin fsica de unos fusibles y slo se podan programar una vez, con todas laslimitaciones que esto supona. Con el paso del tiempo, la tecnologa permiti el borrado odesconfiguracin del dispositivo mediante exposicin a rayos UV o bien elctricamente y,

por tanto, su reconfiguracin.Los dispositivos lgicos programables evolucionaron con la idea de proporcionar al

diseador mayor flexibilidad y posibilidades de configuracin, con lo que incorporaronregistros, realimentaciones a los arraysprogramables, bufferstri-estado, etctera (figura 1.5).

-

8/6/2019 Arquitectura_FPGA

3/12

Figura 1.5. Diagrama lgico de una PAL16R8

La siempre creciente capacidad de los circuitos integrados cre una oportunidad paralos fabricantes de disear PLDs ms grandes para aplicaciones mayores de diseo digital.Sin embargo, un dispositivo demasiado grande usando una estructura alambrada del estilode las figuras 1.4 y 1.5 sera demasiado lento y, desde el punto de vista del fabricante, no sehara un uso efectivo en cuanto al costo del rea del chip [5].

Como escalar esta estructura resultaba irrealizable, los fabricantes idearon undispositivo lgico programable complejo (CPLD) que consista, bsicamente, en unacoleccin de PLD individuales en un simple chip, en compaa de una estructura deinterconexin programable que permita que los PLD fueran conectados entre s en el chip

de la misma manera que un diseador conectara externamente PLDs individuales (figura1.6).

-

8/6/2019 Arquitectura_FPGA

4/12

Figura 1.6. Arquitectura genrica de un CPLD

Actualmente, las compaas Xilinx, Altera y Lattice fabrican CPLDs que difieren enlas PLDs internas (tanto el arrayde puertas AND como en las macroceldas de salida), enlos bloques de entrada y salida, y en la interconexin programable.

1.3. FPGAsLa invencin del microprocesador retras al menos una dcada la aparicin del

primer dispositivo FPGA. Siempre teniendo en mente las ventajas e inconvenientes de los ASIC, Xilinx sac al mercado un Gate Array programable por campo, es decir, lasustitucin de la interconexin fija de los Gate Arrays por una serie de pistas metlicasconectables por transistores de paso controlados por un conjunto de bits de controlalmacenados en una memoria interna. De hecho, la interconexin reconfigurable ya habasido detallada en un artculo de 1967 [6]. As, estos dispositivos surgen en 1985 con elnombre de LCA (Logic Cell Array), aunque posteriormente se renombraron como FPGA(Field Programmable Gate Array)

Arquitectura general

Bsicamente, en una FPGA la lgica se divide en un gran nmero de bloques lgicos

programables que son individualmente ms pequeos que un PLD (figura 1.7 ). Seencuentran distribuidos a travs de todo el chip en un mar de interconexionesprogramables y todo el arreglo se encuentro rodeado de bloques de E/S programables(IOBs). Un bloque lgico programable (CLB o slice) de FPGA es menos eficiente que unPLD tpico, pero un chip FPGA contiene muchos ms bloques lgicos que los PLD quecontiene un CPLD del mismo tamao [5].

-

8/6/2019 Arquitectura_FPGA

5/12

Celda lgica

Bloque de memoria

Multiplicador dedicado

Bloque de E/S

DCM

Buffer de reloj

Figura 1.7. Arquitectura general de una FPGA

Slices: En los slices se realiza la mayor parte de la funcionalidad de la FPGA ysuelen estar agrupados de 2 en 2 o de 4 en 4 formando bloques lgicos

configurables (CLBs). Dentro de este componente encontramos los mdulos

LUT, registros y multiplexores programables en un nmero que depende de

familia de FPGA, pero la arquitectura bsica comn es la que se muestra en la

figura 1.8.

-

8/6/2019 Arquitectura_FPGA

6/12

DQ

SR

CE

DQ

SR

CE

LUTG4G

3

G2

G1

G

LUTF4F

3

F2

F1

F

H

H1

Y

X

YQ

XQ

=multiplexor programable

Figura 1.8. Slicesimplificado de una FPGA

Los elementos programables ms importantes son los generadoresreprogramables de funcin lgica, realizadas por las denominadas LUT (Look-up

Table) o tablas de bsqueda, que son celdas de memoria SRAM y multiplexorespara seleccionar la salida (figura 1.9) [7].

Figura 1.9. LUT de 2 entradas, implementacin de lafuncin (AB)

Los generadores de funcin pueden disearse para cualquier nmero devariables que se desee sin ms que aumentar el tamao de la memoria SRAM y laubicacin de selectores que escojan un solo valor almacenado para cadacombinacin de valores de las variables, de la manera que se muestra en la figura1.10.

-

8/6/2019 Arquitectura_FPGA

7/12

X

X

X

X

SRAM

ab

f

X

X

X

X

X

X

X

X

SRAM

abc

f

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

SRAM

abcd

f

2-LUT

3-LUT

4-LUT

Figura 1.10. LUTs de 2, 3 y 4 variables

Sin embargo, el nmero de variables con que pueden disearse las LUTs noes trivial. Si intentamos realizar una LUT con un nmero de entradas elevado, elrea que ocupara sera relativamente grande, con lo que el nmero de slicesdentro

de la FPGA se reducira. Si, por el contrario, se opta por LUTs con pocas entradas,cabran muchos slices, pero la rutabilidad sera complicada, se necesitaran muchasconexiones por lo que el retardo debido al cableado entre los slicessera importante.Por lo que puede apreciarse en las figura 1.11, parece alcanzarse un compromisoentre el rea y la velocidad usando LUTs de 4 entradas [8].

reanormalizada

R

etrasopromedio(ns)

Figura 1.11. Tamao ptimo de las LUTs

Cualquier funcin lgica que se desee implementar con un nmero devariables mayor se realiza usando varias LUTs, ya que dicha funcin siempre podrponerse en funcin de varias funciones de 4 variables aplicando el conocidoteorema de Shannon las veces que sea necesario [9]:

),,0(),,1(),,( 212121 nnn XXFXXXFXXXXF KKK +=

-

8/6/2019 Arquitectura_FPGA

8/12

En general, los slicescontienen alguna lgica adicional aparte de las LUTs paraaumentar las prestaciones y la eficiencia de estos bloques, como biestables paraobtener salidas registradas o lgica para implementar eficientemente comparadores,contadores o sumadores serie. Adems, como las funciones lgicas se generan enrealidad a travs de memorias SRAM, los propios slicesse pueden configurar para

usarlos como bloques de memoria en lugar de lgica, es lo que se denominamemoria distribuida para diferenciarla de bloques de memoria especficos quepudiera haber en la FPGA. Los slices ms prximos suelen agruparse siguiendo estafilosofa en grupos denominados CLBs o bloques lgicos configurables.

IOBs: Los bloques de Entrada/Salida de las FPGAs cumplen la misma funcinque las macroceldas de salida en otros dispositivos lgicos programables, pero conms controles lgicos, entre los que se incluyen, configuraciones de entrada y salidacombinacionales o registradas, alta impedancia, elementos de retardo, controlesanalgicos y otros.

Interconexin programable: Segn se mostr en la figura 1.7, cada CLB en la

FPGA se encuentra incrustado en la estructura de interconexin, que se componenen realidad de cables con conexiones programables para ellos. Inicialmente, sedispona de unas interconexiones heterogneas de propsito general, aunque en ladcada pasada se evolucion hacia una estructura de interconexin jerrquica, talcomo se muestra en la figura 1.12. Las lneas del grupo del reloj estn optimizadaspara su uso como entradas de reloj a los CLB, proporcionando un retardo corto. Elconjunto de lneas simples se optimizan para conectividad flexible entre bloquesadyacentes, pero en mayor cantidad y sin la limitacin unidireccional de las lneasdirectas.

2

3

3

4

8

4846

2

Simple

Doble

Larga

Conexindirecta

Larga

RelojGlobal

SimpleDobleLarga ConexinDirecta

2

2

CLB

Figura 1.12. Estructura de interconexin de una FPGAXC4000 de Xilinx

Sera posible conectar dos CLBs no adyacentes usando lneas simples, perodeberan pasar por un conmutador programable para cada salto, lo que agregararetardos adicionales. Las lneas de los grupos doble viajan pasados dos CLBs antesde llegar a un conmutador, de modo que proporcionan retardos ms cortos paraconexiones ms largas. Para conexiones muy largas, se emplean los grupos largos,

que no pasan por ningn conmutador programable y recorren todo la FPGA envertical u horizontal.

-

8/6/2019 Arquitectura_FPGA

9/12

Otros componentes dentro de una FPGA: Las FPGAs muchas veces se evalanen funcin de la flexibilidad de sus arquitecturas y la consistencia de los resultadosobtenidos de un ajuste despus de que se han efectuado pequeos cambios dediseo. De esta manera, los fabricantes proporcionan recursos extra en susarquitecturas para ayudar a asegurar resultados consistentes e implementar algunos

sistemas de manera muy eficiente. As, si las FPGAs ms antiguas eran muy homogneas, como las XC4000

[10], las que imperan hoy en da, familias como la Spartan-3 [11-12] o Virtex-4 [13-14], representantes de la gama baja y la gama alta de las FPGA de Xilinxrespectivamente, disponen de diversos dispositivos embebidos dentro deldispositivo, como memorias, multiplicadores, DCMs (administradores de reloj), eincluso microprocesadores.

La FPGA Spartan-3 XC3S200

En la tabla 1.1 se muestran las caractersticas principales del dispositivo que puede

extraerse de las especificaciones del fabricante. En este caso se dispone de 2 columnas de 6multiplicadores integrados en el dispositivo. Tambin se dispone de 12 bloques de 18Kbitsde RAM. En esta familia, los slicesse agrupan de 4 en 4 formando los CLBs, teniendo unarrayde 24x20 de estos bloques. Cada slicecontiene 2 generadores de funcin (LUT) y 2flip-flops, acorde con la figura 1.8.

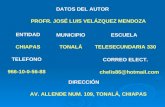

Caractersticas de la Spartan-3 XC2S200

General Recursos CLBsPuertas equivalentes 50K Filas 24

DCMs 4 Columnas 20CLBs 480 Total 480

Pines E/S 173 Slices 1920Multiplicadores 12 LUTs/Flip-Flops 3840

Mdulos BRAM RAM16/SRL16 1920Columnas de RAM 2 Memoria distribuida 30K

Bloques de RAM por columna 6Bloques de RAM 12

Memoria RAM disponible 216K

Tabla 1.1. Caractersticas principales de la Spartan-3XC3S200

Cada LUT puede configurarse como una memoria de 16x1 bits o como un registro

de desplazamiento que puede ser de 16 bits como mximo. Configurados como memoriadistribuida, se puede almacenar hasta 30Kbits.

La FPGA Virtex-4 XC4VSX35

Examinando los datos de la tabla 1.2 podemos observar que la Virtex-4 poseemayores recursos que la Spartan-3. En el caso de este dispositivo los multiplicadores hansido sustituidos por unos circuitos aritmticos ms completos denominados DSP48s y

vienen en mayor cantidad. Nuevamente los slices se asocian cada 4 formando un CLB,aunque estos difieren ligeramente de los que forman parte de la Spartan-3 y se dispone demayor cantidad de memoria, tanto en mdulos especficos (tambin de 18Kbits) como enmemoria distribuida.

Caractersticas de la Virtex-4 XC4VSX35

General Recursos CLBs

-

8/6/2019 Arquitectura_FPGA

10/12

Celdas lgicas 34560 Filas 96DCMs 8 Columnas 40CLBs 3840 Total 3840

Pines E/S 448 Slices 15360DSP48s 192 LUTs/Flip-Flops 30720Mdulos BRAM RAM16/SRL16 15360

Columnas de RAM 8 Memoria distribuida 240KBloques de RAM por columna 24

Bloques de RAM 192Memoria RAM disponible 3456K

Tabla 1.2. Caractersticas principales de la Virtex-4XC4VSX35

Circuitos aritmticos especficos en FPGA

Algunos de los componentes especficos que ms xito estn teniendo dentro de lasFPGAs son aquellos pensados para resolver de manera eficiente clculos matemticoscomplejos. Segn qu FPGA analicemos podemos tener circuitos aritmticos distintos, yaque estos se van mejorando segn van apareciendo nuevas familias. Por ejemplo, laSpartan-3, contiene unos mdulos denominados MULT18x18 bastante sencillos. La Virtex-4, en cambio, contiene un mdulo ms avanzado, el DSP48, con mayores prestaciones. Lafamilia ms potente que tiene Xilinx en el mercado, la Virtex-5, dispone de bloques DSP48mejorados, los denominados DSP48E.

Circuitos MULT18x18

Se trata de multiplicadores de nmeros de 18 bits en complemento a dos. Elresultado tiene una precisin de 36 bits. A continuacin, en la tabla 1.3 se muestraen el nmero de estos circuitos en las FPGAs de la familia Spartan-3:

Spartan-3

Dispositivo Multiplicadores

XC3S50 4XC3S200 12

XC3S400 16XC3S1000 24XC3S1500 32XC3S2000 40XC3S4000 96XC3S8000 104

Tabla 1.3. Nmero de multiplicadores en diferentesSpartan-3. En negrita aparece la FPGA disponible en ellaboratorio

Circuitos DSP48

Estos circuitos proporcionan un mayor nivel de integracin de procesado deseales que las anteriores FPGAs del fabricante. Se suele disponer de un buennmero de estos circuitos teniendo en mente un empleo mnimo de lgica genricaadicional, lo que conlleva a un menor consumo, alto rendimiento en trminos de

velocidad, y un uso eficiente de los recursos del dispositivo [15]. La figura 1.13

muestra dos circuitos DSP48. Estos mdulos aparecen asociados en parejas puescomparten el puerto C, adems de lneas de interconexin dedicadas.

-

8/6/2019 Arquitectura_FPGA

11/12

Figura 1.13. Aspecto de dos DSP48

El mdulo fundamental de este circuito es el multiplicador 18x18 de nmerosen complemento a dos. Este multiplicador viene acompaado de unsumador/restador/acumulador de 48 bits, el cual es necesario en multitud deaplicaciones dentro del procesado digital de seal. El resto de componentes de lafigura proporcionan una enorme posibilidad de configuracin del circuito, lo que serevierte una gran versatilidad y alta velocidad de funcionamiento. De esta manera,el DSP48 puede implementar funciones matemticas bsicas de manera sencilla y aalta velocidad, como sumadores/restadores, acumuladores, varios tipos demultiplicadores, multiplicadores/acumuladores (MAC), multiplexores,desplazadores, contadores, divisores y races cuadradas. As, la asociacin de variosde estos circuitos se presenta como un recurso muy potente para la implementacinde funciones avanzadas de manera eficiente [16].

A continuacin se muestra, en la tabla 1.4, los DSP48 que disponen lasdistintas FPGAs de la familia Virtex-4.

-

8/6/2019 Arquitectura_FPGA

12/12

Virtex-4

Sub-Familia LX Sub-Familia SX Sub-Familia FX

Dispositivo DSP48 Dispositivo DSP48 Dispositivo DSP48

XC4LX15 32 XC4VSX25 128 XC4VFX12 32XC4LX25 48 XC4VSX35 192 XC4VFX20 32

XC4LX40 64 XC4VSX55 512 XC4VFX40 48XC4LX60 64 XC4VFX60 128XC4LX80 80 XC4VFX100 160XC4LX100 96 XC4VFX140 192XC4LX160 96XC4LX200 96

Tabla 1.4. Nmero de DSP48s en diferentes Virtex-4. Ennegrita aparece la FPGA disponible en el laboratorio

La familia Virtex-4 SX ofrece la ms alta relacin de DSP48s frente a slices, asque sta es la familia adecuada para realizar aplicaciones donde existe un alto

componente matemtico.