EE441F6

-

Upload

daniel-uculmana-lema -

Category

Documents

-

view

2 -

download

0

description

Transcript of EE441F6

LABORATORIO DE CIRCUITOS ELECTRÓNICOS I

EXPERIENCIA No6

AMPLIFICADOR CON TRANSISTOR FET

INFORME FINAL

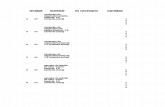

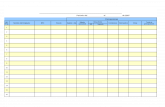

1. Presentar las mediciones efectuadas en un circuito en una hoja completa con todas las indicaciones (circuito original).

Ckto. Original RS=1K RS=5.6K RS=3.3K y RD=5.6K

VD 6.65V 1.57V 8.53V 8.81V VS 1.34V 0.95V 1.43V 1.35VVG 10mV 10mV 10mV 10mVVDS 5.57V 0.62V 7.1V 8.6V

Circuito 1

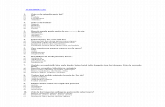

2. Trazar la curva de transferencia Id - vs - Vgs indicando los puntos de operación de la tabla llenada y las rectas de polarización ID = (-1/Rs).Vgs, obtenidas de Vgs = -ID.Rs, por inducción de la curva aproximar los datos del FET como son : IDSS y VPO . Explicar las observaciones que diera a lugar.

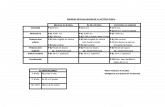

Haciendo el respectivo analices y calculando la corriente ID:Tenemos VGS = VG - VS = 0 - Vs = -Vs

VGS = -ID.Rs => ID1 = -VGS / Rs

También se puede calcular VDD = VD + ID.RD => ID2 = (10 - VD)/RD

Cto Original Rs = 1K Rs = 5.6K Rs = 3.3K y RD = 5.6KID2 0.335 mA 0.843mA 0.147 mA 0.2125 mAID1 0.406 mA 0.95 mA 0.255 mA 0.409 mAVs (v) 1.34 0.95 1.43 1.35VG (v) » 0 » 0 » 0 » 0

También sabemos ID = IDSS.(1-VGS/Vp)2 , tenemos considerando los datos del Jfet que los valores de: IDSS = 4mA y Vp = 4V

Calculando el punto Q.

VGSQ = - Rs.IDQ = -3.3.IDQ, también

IDQ/ IDSS = (1-VGS/Vp)2 => IDQ / 4m = (1-(-3.3 IDQ / 4))2

IDQ = 365.2mA

VGSQ = -3.3(365.2m) = -1.205 V

Calculando Av.gm = -2 (IDSS / Vp). (1- VGSQ / Vp) = -1.3975mrd = 1/ gm = 0.715K

Av = -(RDççRL)/(Rsca+1/gm) =1.911

Para trazar las gráficas de la curva de transferencia, necesitamos de los siguientes datos:

Cto Original Rs = 1K Rs = 5.6K Rs = 3.3K y RD = 5.6KID1 0.406 mA 0.95 mA 0.255 mA 0.409 mAVGS (v) 1.34 0.95 1.43 1.35

3. Trazar la curva de salida ID vs VDS indicando los puntos de operación obtenidos. Indicar la zona del transistor y la recta de carga en cada caso.

Cto Original Rs = 1K Rs = 5.6K Rs = 3.3K y RD = 5.6KVDS 5.57V 0.62V 7.1V 8.6VID1 0.406 mA 0.95 mA 0.255 mA 0.409 mA

4.Explicar porque se limita Vomax sin distorsión de la señal.

Se limita Vomax para poder determinar el rango de Vi en el cual va ha funcionar el circuito que si por alguna razón este voltaje Vi se pasa de los valores establecidos, la onda en la salida estará distorsionada, originando daños en dispositivos que hay en el circuito del amplificador. También lo hacemos limitar Vi para poder usar un rango de voltajes de salida en el amplificador del FET sin distorsión.

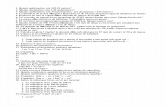

5. Dibujar la curva 20log(Av) vs log(f) (respuesta en frecuencia)

f(Hz) 50 100 200 500 1000 2K 5K 10K 20K 50K 100K 200K 500KVo(v) 0.18 0.26 0.26 0.30 0.26 0.26 0.26 0.24 0.24 0.24 0.26 0.20 0.1220logAv 19.08 22.27 22.27 23.52 22.27 22.27 22.27 21.58 21.58 21.58 22.27 20 15.56logf 1.69 2 2.30 2.69 3 3.30 3.69 4 4.30 4.69 5 5.30 5.69

Nota . En la medición Vo, en cada frecuencia ,obtuvimos dos valores uno positivo y uno negativo por ejemplo para 50Hz, en el osciloscopio vimos

Vo+ = 0.20 Vo- = 0.16

Hemos hecho el promedio de los dos para obtener 0.18V, como se muestra en el cuadro.

Teóricamente la curva de 20log(Av) - log(f), debería ser una curva que haciende a bajas frecuencias, luego se mantiene constante y decrece, pero esto no es así por los condensadores no son de valores muy grandes; comportandose a baja frecuencia como una impedancia en baja frecuencia, por lo tanto habría una caída de tensión., en le caso ideal seria que la capacitancia en los condensadores sean muy grandes (C® ¥), este caso no importa los condensadores por estos en cualquier valor de frecuencia se convertirán en corto circuito y la curva 20log(Av)-log(f) seria en realidad la curva de respuesta en frecuencia del transistor.

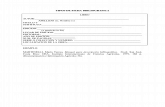

6. Explicar la ganancia obtenida en el paso 6.

Observamos lo siguiente.

Av = 40mV/20mV = 2

Observamos que la ganancia es poca esto es debido a que este condensador Cs hace que la ganancia aumente y este no esta en el circuito la ganancia disminuye.

Entonces la ganancia teóricamente seria

Av = -gm(RD//RL).

OBSERVACIONES Y CONCLUSIONES.

* De este ultimo paso podemos concluir que que el condensador Cs hace que la ganancia en la salida Vo aumente la señal de entrada Vi.

* Hay que hacer una observación es que en este caso hemos utilizado capacitores de 10uf , 22uf y no de valores grandes para que la señal en ac pase como si fuera un corto circuito, y no hayga una impedancia que provoca una caída de tensión,

* Podemos tener en cuenta que en los transistores FET tienen un menor nivel de ruido que los BJT. Esto se pudo observar cuando vimos en el osciloscopio la onda era más liza comparada con el BJT que te amplificaba con todo y ruido.

* Se puede concluir que para Rs=1K el FET se comportaba como un resistor variables controlados por tensión. Con este valor de resistencia nos encontrábamos en la Zona Ohnmica del transistor FET.

* L alta impedancia de entrada de los FET les permite almacenar carga el tiempo suficiente para permitir su utilización como elementos de almacenamientos.

* Los FETs son más estables con la variación de la temperatura que los BJT.

* Los FET de potencia pueden disipar una potencia mayor y conmutar corrientes grandes.

*************************