Jerarquía Digital Plesiócrona2

Transcript of Jerarquía Digital Plesiócrona2

Jerarqua Digital PlesicronaJDP-PDH

Resumen Introduccin. Revisin multiplex-sincronismo. Multiplexacin PDH europea. Sincronismo en PDH. Justificacin en PDH. Niveles superiores PDH europea. Conclusiones. Ventajas y desventajas.

Introduccin PDH surgi para redes de telefona, con el objetivo de que varios canales telefnicos compartieran el mismo medio de transmisin utilizando tcnicas de multiplexacin por divisin en tiempo. En la clase anterior vimos la trama E1, que es el nivel bsico de multiplexacin que se define dentro de la PDH. A partir de la multiplexacin de estas tramas bsicas se originan tramas de orden superior, que permiten transportar ms canales de voz sobre un mismo medio de transmisin y, por lo tanto, lograr un uso ms eficiente de los anchos de banda disponibles.

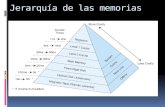

Especificaciones de la PDH existentes: Existen 3 jerarquas plesicronas. La jerarqua europea utiliza la trama definida en la Rec. G.732 como trama bsica. Agrupa 30+2 canales de 64 kb/s para obtener 2.048 kb/s. Luego, por multiplexado de 4 tributarios sucesivamente, se obtiene las velocidades de 8.448 kb/s; 34.368 kb/s y 139.264 kb/s.

Especificaciones de la PDH existentes: Las otras dos jerarquas utilizan la Rec. G.733 La jerarqua norteamericana agrupa 24 canales a una velocidad de 1.544 kb/s. Posteriormente genera 2 ordenes superiores (x4) a 6.312 kb/s y (x7) a 44.736 kb/s. La jerarqua japonesa recupera el valor de 6.312 kb/s pero obtiene los rdenes jerrquicos de (x5) 32.064 kb/s y (x3) 97.728 kb/s.

rdenes de las Jerarquas y velocidades asociadas. La jerarqua de 1544 y 2048 kb/s se diferencian tanto en la codificacin como en la trama. La norma de facto de 24 canales que da origen a 1544 kb/s se deriva del hecho que la Bell Labs (1960) pretendi mantener la compatibilidad con el sistema de 24 canales FDM.Orden

USANx45MbpsxN

EUROPA140 Mbpsx3x4

4 3 2 1

45 Mbpsx7

34 Mbpsx4

6.3Mbpsx3 x4

8 Mbpsx4

1.5Mbpsx24 x30

2 Mbps

64 kbps

Histrico de la PDH norma europea. En lugar Europa, algunos aos ms tarde (1965), se cambi la codificacin (ley por la ley A) e incorpor la velocidad de 2048 kb/s para adoptar una potencia de 2.

Sincronismo Los sistemas de transmisin digital tienen en cuenta el sincronismo en varios niveles: Sincronismo de bit: se refiere a que el receptor pueda conocer exactamente dnde comienza y termina un pulso de seal correspondiente a un bit enviado por el transmisor. Sincronismo de trama: se refiere a que el receptor pueda interpretar correctamente el significado de la secuencia de bits recibida del canal.

Sincronismo de bit Puede lograrse de dos maneras fundamentales: Que el receptor y transmisor tengan un reloj de referencia comn, o Que el transmisor tenga un reloj y el receptor sea capaz de obtener la seal de reloj del transmisor a partir de la seal de informacin que le est llegando. Para esta 2da variante se han desarrollado cdigos de lnea como el HDB3, que permiten desarrollar esta funcionalidad.

Sincronismo de trama Se logra a partir de palabras de alineacin, que indicarn el inicio de una trama y, a partir del conteo, el receptor puede interpretar el significado de los dems bits.

Importancia del sincronismo No slo es importante para entre transmisor y receptor (multiplexor y demultiplexor), de un mismo nivel, sino tambin entre multiplexores de distintos niveles, para la multiplexacin de tramas de orden inferior (tributarios), tales como un E1, en tramas de orden superior (agregadas) como un E4. El multiplexor de nivel superior es receptor de la seal transmitida por el multiplexor de orden inferior. Podemos resumir que en los sistemas de transmisin digital el rol de transmisor lo realiza siempre el multiplexor, el rol de receptor lo realizan el demultiplexor del mismo nivel y el multiplexor de orden superior.

Problemas de Sincronismo Relojes imperfectos: el uso de relojes con una misma frecuencia nominal en los nodos del sistema no garantiza que tengan la misma frecuencia real, que se corresponde con la frecuencia instantnea del reloj. Este fenmeno es conocido como fluctuacin o deriva de frecuencia. Fluctuacin de fase: fenmeno conocido como jitter. Implica un desplazamiento de los bits en el tiempo, es decir, que los bits no llegan en el momento que se les espera (lo cual no implica que no lleguen con la frecuencia que se les espera), sino que su llegada se retrasa. El agravamiento de este fennemo es acumulativo con el aumento de la distancia de la lnea y con la cantidad de regeneradores intermedios. Variacin del retardo de transmisin: esto implica que la seal sufra retardos variados (variacin del jitter) debido a condiciones ambientales, a reencaminamientos en la red, a variaciones de la longitud del camino de propagacin, etc.

Deslizamientos de trama y soluciones. El slip es provocado por diferencias de frecuencia instantnea entre los relojes del transmisor y el receptor. Se caracteriza por la doble lectura de un bit enviado por el transmisor. Puede ocurrir: Cuando la frecuencia de lectura del receptor es mayor que la frecuencia de envo del transmisor, o Por la prdida de un bit en la lectura, que puede ocurrir cuando la frecuencia de lectura del receptor es menor que la frecuencia de envo de los bits.

Es significativo cuando el receptor de los bits es un multiplexor de orden superior. Para evitar este efecto se emplean en estos tipos de dispositivos, memorias elsticas y el proceso de justificacin.

Memoria elstica Para solucionar parcialmente estas diferencias de frecuencia, los receptores utilizan memorias o buffers para almacenar provisionalmente los bits que llegan de la lnea con determinada frecuencia, que luego sern ledos a una frecuencia distinta. Estas memorias son conocidas como memorias elsticas. Son 2 registros o memorias conectadas sucesivamente en serie con cada estado de memoria (flip-flop) en paralelo. Los datos se escriben en forma cclica en el registro de entrada mediante un reloj de escritura CKE coherente con los mismos datos. La lectura se realiza con un reloj CKL distinto. Si estas diferencias de frecuencia se mantienen de forma sostenida en un solo sentido, cada cierto tiempo la memoria se llenar o se vaciar, siendo imposible solucionar el problema.

Justificacin (stuffing) Trata de adaptar la velocidad de lectura de la memoria a la velocidad de escritura en la memoria. Bits de justificacin: son bits extra contenidos en la trama de salida de multiplexores de niveles superiores, que se utilizan para la adaptacin de las velocidades de lectura. Estos bits pueden llevar informacin proveniente de la seal de entrada o relleno y su uso supone el empleo de bits de control de justificacin para informar al receptor (demultiplexor) del contenido de esos bits.

Justificacin positiva Ocurre cuando la lectura es ms rpida que la escritura en la memoria. Para evitar que la memoria se vace, se enva relleno en los bits de justificacin positiva, que en condiciones normales (si las frecuencias de lectura y escritura fueran iguales) llevaran informacin.

Justificacin negativa Ocurre cuando la lectura es ms lenta que la escritura en la memoria. Para evitar que la memoria se llene, se enva informacin en los bits de justificacin negativa, los cuales, en condiciones normales (si las frecuencias de lectura y escritura fueran iguales), llevaran relleno.

Desviacin entre frecuencias instantneas La capacidad de justificacin impondr lmites de desviacin entre relojes y la capacidad de la memoria debe calcularse en concordancia, para que no se pierdan bits. Esta desviacin entre frecuencias instantneas que el sistema es capaz de soportar se expresa en partes por milln ppm. Por ejemplo: en una lnea de 2048 kbps se permiten desviaciones de 50 ppm, es decir, variaciones de 200 bps de la velocidad nominal del flujo.

Modos de operacin Sncrono: Todos los relojes del sistema estn controlados por un mecanismo automtico que garantiza su operacin a la misma frecuencia nominal. Se utilizan 1 o 2 relojes de alta calidad que diseminan la informacin de temporizacin mediante una red de control de sincronizacin. La jerarqua digital sncrona sigue este modo.

Modos de operacin Plesicrono: Cada reloj del sistema opera de forma independiente. Es necesario entonces utilizar relojes de alta estabilidad y resintonizarlos peridicamente de forma manual con el fin de que operen dentro de unos lmites cercanos a la frecuencia nominal de la red. En estos sistemas se utilizan los mecanismos de justificacin vistos anteriormente. La jerarqua digital plesicrona sigue este modo.

Multiplexacin en PDH norma europea

Caractersticas de la PDH norma europea. Los multiplexores de niveles superiores siempre multiplexan 4 tramas de orden inferior. (PDH norma europea) La multiplexacin de orden superior se realiza bit a bit. Esto constituye una de las desventajas de la PDH, pues para obtener una trama E1 determinada contenida en una trama de orden superior por ejemplo de nivel E4, ser necesario demultiplexar todos los niveles de la jerarqua intermedios hasta llegar al nivel de la trama que se quiere obtener. La multiplexacin del nivel bsico es la nica que se realiza byte a byte.

Caractersticas de la PDH norma europea. Las velocidades de cada orden es levemente superior (en un 1% aprox.) al producto de la velocidad de un tributario multiplicado por el nmero de tributarios, debido al agregado de informacin adicional (OverHead). La informacin adicional incluye, bits de control (alineacin, alarma y bits de control de justificacin) y bits de justificacin. A la jerarqua se le denomina plesicrona (casi sncrona) porque los relojes usados por los nodos del mismo nivel de la jerarqua son independientes y en consecuencia, los relojes para conformar las tramas de los distintos niveles de la jerarqua tambin son independientes entre s.

Sincronismo en PDH Entre multiplexor-demultiplexor de un mismo nivel de la jerarqua: es necesario garantizar el sincronismo en los dos niveles: Sincronismo de trama: se logra con el mecanismo de alineacin basado en la palabra de alineacin de trama transmitida al inicio de la trama. Sincronismo de bit: el multiplexor transmite la seal del reloj con el cual conform la trama, a travs del cdigo de lnea con el cual se codific la trama. Esa seal es recuperada por el demultiplexor y utilizada para la lectura de los bits y para poner los bits en sus interfaces de salida. A este mtodo de sincronismo se le conoce como Sincronismo Mutuo.

Sincronismo en PDH Entre multiplexor de orden inferior-multiplexor de orden superior: slo es necesario garantizar el sincronismo a nivel de bit, puesto que el multiplexor de orden superior no necesita conocer dnde empieza y termina una trama de orden inferior. Sincronismo de bit: cada tributario a la entrada del multiplexor de orden superior, lleva consigo su propia seal de reloj con la cual fue conformado, a travs del cdigo de lnea. Estas seales a la entrada del multiplexor de orden superior, son seales plesicronas. Para su lectura desde el canal y su escritura en la memoria elstica, el multiplexor obtiene de cada una de ellas la seal de reloj y las lee de forma independiente utilizando la seal de reloj recuperada. En este paso del proceso tambin se utiliza el mtodo de Sincronismo Mutuo.

Justificacin en PDH A la salida del multiplexor existe un flujo de velocidad constante, por lo tanto la multiplexacin debe realizarse a velocidad constante. Se debe fijar una velocidad de multiplexacin, para cada tributario se adapta esta velocidad por medio de la justificacin.

Justificacin Positiva Para acomodar las seales de entrada plesicronas, en la del multiplex de orden inmediato superior se les asigna a cada una, una capacidad de transmisin mayor que la que necesita el afluente si su velocidad es igual a la nominal (en la prctica de 0.1 a 0.2 %). Esto es, que la velocidad del multiplex para cada una de las seales de entrada se fija a un valor mayor que la velocidad que se necesitara si llegara con una velocidad igual a la nominal. Esta capacidad extra se logra a partir de la insercin de bits de justificacin en la trama de salida del multiplex.

Justificacin Positiva Para conformar el E2 se fija la velocidad del multiplex de cada tributario de Vnominal=2048 kbps a una f=2052 kHz, que corresponde a una capacidad disponible a la salida de 2052 kbps.1

MEMORIA ELASTICA

ESCR.

LECT.

Ck1 2048 kbps

Inhibir Lectura

Ck2 2052 kbps

Cj

Justificacin Positiva El uso de bits extra, por lo general es 1 bit extra por trama para cada afluente, depender de la velocidad del afluente. La justificacin depender del defasaje entre los relojes de la seal tributaria y del reloj fijado para cada afluente en base a la capacidad de salida asignada a cada uno. Si el afluente tiene una velocidad mxima, de 2052 kbps para el caso de E1, entonces todos los bits de justificacin de ese afluente llevarn informacin vlida, ocupando la capacidad mxima disponible. Si el afluente tiene una velocidad igual a la nominal, 2048 kbps para el caso de E1, entonces existirn bits de justificacin con informacin y otros con relleno.

Los bits de control de relleno son los encargados de avisar al demultiplexor cules bits de justificacin llevan informacin y cules llevan relleno.

Justificacin positiva/nula/negativa La capacidad asignada a cada afluente en la seal multiplex de salida coincide con la que necesita si su velocidad es la velocidad nominal, de 2048 kbps para el caso de E1. Si la velocidad del afluente es exactamente igual a la nominal, entonces no se efecta relleno, los bits extra para la justificacin positiva llevarn informacin y los bits extra para la justificacin negativa llevarn relleno. Si la velocidad del afluente es menor que la nominal, se efecta justificacin positiva y los bits extra para la justificacin positiva llevarn relleno Si la velocidad del afluente es mayor que la nominal, entonces se efecta justificacin negativa y los bits extra para la justificacin negativa llevarn informacin.

Este tipo de procedimiento slo est definido para usarse en el nivel 2 de la jerarqua norma europea.

Niveles superiores de la PDH norma europea. Existen 2 tipos de trama E2, con justificacin positiva y con justificacin positiva/nula/negativa definidas en las Rec. G.742 y G.745 respectivamente. La ms utilizada es la G.742.

Trama E2 G.742 Se compone de 4 grupos de 212 bits, o sea un total de 848 bits por trama. El primer grupo comienza con la palabra de alineacin de trama de 10 bits, luego siguen 2 bits de servicio y 200 bits de afluentes, entrelazados, en sucesin cclica. Los otros 2 grupos siguientes tienen la misma composicin, 4 bits para el control de justificacin cada uno y luego 208 bits de afluentes. El ltimo grupo tiene 4 bits primeros para el control de la justificacin y 4 bits siguientes para la justificacin positiva, es decir, 1 por afluente en cada trama, los restantes 204 bits son para los afluentes.

Trama E2 G.742 Por afluente tenemos: 1 bit de justificacin positiva, es decir, que puede llevar informacin o relleno 205 bits de informacin de afluente, y 3 bits para el control de la justificacin.

Estos 3 bits de control de justificacin son para decirle al receptor si el bit de justificacin lleva informacin de afluente o relleno y no incurrir en errores que puedan provocar deslizamientos de tramas. La decisin se toma por mayora, son 3 bits, si los 3 llevan 111, se decide que hay relleno. Ahora si ocurri un error que hizo que uno de ellos cambiara su valor a 0, de todas maneras, por mayora de unos, el receptor decide que hay relleno.

Anlisis de velocidades. La velocidad mxima soportada por el nivel E2 para cada uno de sus afluentes E1 coincide con la capacidad mxima permisible. Esta capacidad se alcanza cuando los bits de justificacin correspondientes a un afluente tambin llevan informacin, es decir, todos los bits de justificacin de un afluente de todas las tramas que pasan en 1 segundo, deben llevar informacin.

Anlisis de velocidades. Existe 1 bit de justificacin por afluente en cada trama E2, slo nos queda saber cuntas tramas E2 pasan en 1 segundo. La velocidad del E2 es de 8448 kbps y que la trama lleva 848 bits, de aqu podemos calcular la cantidad de tramas en 1 segundo o lo que es lo mismo, la frecuencia de trama fT = 8448x103/848 9962.264 tramas/s. Entonces en 1 segundo 1 afluente tiene 9962.264 bits de justificacin. Puede calcularse tambin la cantidad de bits del afluente en 1s: bpA/s = fT *bpA/trama. El valor de bpA/trama = 205 y entonces bpA/s= 2042264. Sumando la cantidad de bpA/s ms la cantidad de bits de justificacin/s, tendremos el valor de capacidad mximo, que es de 2052226 bps, es decir, 2052.226 kbps.

Anlisis de velocidades. Si la velocidad del afluente es la nominal. Deben existir 2048 kbps con informacin de afluente. Cuando todos los bits de justificacin en 1 segundo llevan relleno, existirn en 1 segundo 204264 bits con informacin de afluente, que es menor que 2048000. Si todos los bits de justificacin en 1 segundo llevan informacin de afluente, existirn en 1 segundo 2052226 bits con informacin de afluente, que es mayor que 2048000. Por lo tanto, para poder tener 2048000 bits con informacin en 1 segundo, es preciso que algunos de los bits de justificacin en 1 segundo lleven informacin y otros lleven relleno.

Anlisis de velocidades. Cmo calculamos los que llevarn relleno? Restando al mximo de bits con informacin 2052226, la cantidad de bits con informacin requeridos, 2048000 y esto nos dar la cantidad de bits que ahora tendrn relleno, 4226. Es decir, que existirn 4226 bits de justificacin en 1 segundo que llevarn relleno. A esto se le denomina frecuencia nominal de relleno y su valor ser, para la velocidad nominal del afluente, de 4.26 kbps.

Resumen y Conclusiones Existen 2 jerarquas, una basada en la velocidad de 1544 kbps empleada en EUA y Japn y la otra basada en la velocidad de 2048 kbps usada en Europa y Latinoamrica Los niveles superiores se obtienen de la multiplexacin de seales plesicronas del nivel jerrquico inmediato inferior y la tcnica de multiplexacin se conoce como pulse stuffing o relleno de pulso.

Resumen y Conclusiones El primer nivel de multiplexacin se trata bajo la forma de octetos. Los segundo, tercero y cuarto niveles se trabajan bajo la forma de bits. La longitud de las tramas no es uniforme y la duracin es diferente para cada nivel de la jerarqua. El sincronismo de las tramas se obtiene mediante una palabra de alineamiento de trama.

Resumen y Conclusiones No todas las interfaces estn estandarizadas (por ejemplo la ptica). Baja capacidad de los canales (bits) de servicio. La forma de multiplexacin a niveles superiores al cuarto no est estandarizado por la norma. Recoleccin de alarmas, canales de supervisin y servicio no normalizados.

Investigacin Sincronismo Mutuo. Aplicacin para PDH. Desventajas de PDH.