Manual_en_PDF

-

Upload

francisco-perez -

Category

Documents

-

view

98 -

download

7

Transcript of Manual_en_PDF

INSTITUTO TECNOLGICO Y DE ESTUDIOS SUPERIORES DE MONTERREY CAMPUS MONTERREY DIVISIN DE INGENIERA Y ARQUITECTURA DEPARTAMENTO DE MECATRNICA Y AUTOMATIZACIN

LABORATORIO DE DISEO DE SISTEMAS LGICOS(MR00-034)

MANUAL DEL CURSO

Dr. Jorge Limn Robles Francisco Calleja Bernal M.Colaborador: Luis Rosas Cobos

Revisin 01 (Diciembre 2002)

ITESMContenido Planeacin del curso Normas del laboratorio Evaluacin del laboratorio Rbrica Prctica 1: Compuertas Digitales bsicas TTL Prctica 2: Otros Circuitos Combinatorios comunes Prctica 3: Otros Circuitos Combinatorios comunes

Departamento de Mecatrnica y Automotizacin

Prctica 4: Sntesis de circuitos combinatorios y construccin con lgica alambrada Prctica 5: Construccin de circuitos combinatorios con PLDs Prctica 6: Memorias y Flip-flops Prctica 7: Circuitos de tiempo y otros circuitos secuenciales comunes. Prctica 8: Aplicaciones de los FFs Prctica 9: Sntesis de circuitos secuenciales sncronos Prctica 10: Control Lgico Neumtico Prctica 11: Control Lgico Elctrico Prctica 12: Diseo e implementacin de circuitos lgicos mediante PLC Prctica 13: Diseo e implementacin de circuitos lgicos en PLC mediante Grafcet

Laboratorio de Diseo de Sistemas Lgicos

ITESM

Departamento de Mecatrnica y Automotizacin

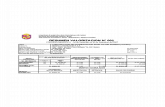

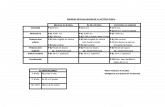

Programa tentativo para el curso y el laboratorio de Diseo de Sistemas Lgicos Profesor: Instructores de laboratorio: Dr. Jorge Limn Robles M. Sc. Armando Cspedes M. Sc. Ral Estrada Laboratorio de Diseo Sistemas Lgicos Presentacin P1: Compuertas Digitales bsicas TTL P2: Otros Circuitos Combinatorios comunes P3: Otros Circuitos Combinatorios comunes P4: Sntesis de circuitos combinatorios y construccin con lgica alambrada ( incluyendo transductores de entrada y salida) P5: Construccin de circuitos combinatorios con PLDs Proyecto 1: Circuito Digital combinatorio P6: Memorias y Flip-flops P7: Circuitos de tiempo y otros circuitos secuenciales comunes. P8: Aplicaciones de los FFs P9: Sntesis de circuitos secuenciales sncronos con PLDs. Proyecto 2: Circuito digital secuencial P10: Circuitos Lgicos neumticos P11: Circuitos Lgicos Elctricos P12: Programacin Bsica de PLCs P13: Programacin Avanzada de PLCs

Semana 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

Diseo Sistemas Lgicos Introduccin Funciones lgicas Sistemas Numricos Sistemas Numricos Algebra Booleana Mapas de Karnaugh Mapas de Karnaugh Sntesis de circuitos combinatorios Construccin con NANDs Primer examen parcial Constr. de circuitos comb con PLDs Constr. de circuitos comb con PLDs (Sol Ex) Constr. de circuitos comb con PLDs Conceptos Bsicos de Circ. Secuenciales Memorias y flip-flops Otros dispositivos secuenciales Anlisis de circuitos secuenciales Anlisis de circuitos secuenciales Segundo examen parcial Sntesis de circ. secuenciales Sntesis de circ. Secuenciales (Sol Ex) Sntesis de circ. secuenciales Circuitos Lgicos Neumticos Circuitos Lgicos Neumticos Circuitos Lgicos Neumticos Circuitos lgicos elctricos Circuitos lgicos elctricos PLC`s Tercer examen parcial PLCs PLCs (Sol Ex) PLCs Tpicos Avanzados Tpicos Avanzados

Laboratorio de Diseo de Sistemas Lgicos

ITESMNormas para el laboratorio 1. Sobre puntualidad y asistencia 2.

Departamento de Mecatrnica y Automotizacin

Se tomar lista 5 minutos despus de la hora de entrada Se considera retardo el llegar despus de haber sido nombrado por primera vez en la lista Acumular 2 retardos es equivalente a una falta 30 minutos despus de la hora de entrada ya no se permitir la entrada al laboratorio El nmero mximo permitido de faltas es el equivalente a 2 semanas. A la prctica que no se asista no se permitir entregar el reporte y la calificacin ser cero en dicha prctica Es responsabilidad de los alumnos y su instructor pactar una fecha de reposicin en caso de no tener sesin por causa de un asueto.

Sobre el cuidado del equipo Todos los alumnos debern cuidar el equipo de trabajo Cualquier dao a los equipos, por un mal uso, ser pagado por los alumnos responsables

3.

Sobre los reportes

El alumno deber entregar un reporte de cada prctica bajo los siguientes lineamientos: Los reportes sern entregados en hojas blancas tamao carta (pueden ser en papel usado previamente) La totalidad o una parte de stos pueden ser hechos a mano siempre y cuando se haga con claridad y limpieza, cuando se hagan dibujos se deber utilizar regla Los reportes debern incluir: o Encabezado (no hay portada) o Objetivo (expresado con sus propias palabras) o Breve descripcin de la prctica (expresada con sus propias palabras) o Desarrollo (datos, clculos, figuras, tablas, etc) o Conclusiones individuales Los reportes sern desarrollados en equipos de dos o tres personas. La calidad y entrega a tiempo del escrito es responsabilidad de todo el equipo. Los reportes debern ser entregados por escrito al instructor, una sesin despus de haber sido realizada la prctica, en el da y la hora en que se cursa el laboratorio El alumno que se retrase en entregar su reporte podr hacerlo a la semana siguiente y su calificacin se asignar con base en un mximo de 70 sobre 100. Despus de una semana de retraso ya no se aceptar. Cualquier indicio de copia en los reportes, prcticas, etc., y/o actos de deshonestidad acadmica se manejarn de acuerdo al reglamento acadmico del ITESM. Si un alumno desea revisin de la evaluacin de su reporte deber manifestarlo al instructor en un periodo mximo de 1 semana despus de haber recibido su reporte calificado. 4. Sobre responsabilidades generales Cada equipo tiene la obligacin de llevar a cada sesin una impresin del desarrollo de la prctica De ser indicado por su instructor, los equipos de trabajo se rotarn. De ser necesario los proyectos podrn ser revisados fuera de clase.

Laboratorio de Diseo de Sistemas Lgicos

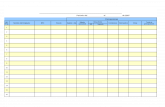

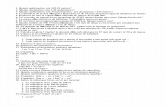

ITESMEvaluacin del laboratorio de diseo de sistemas lgicos Calificacin de la prctica

Departamento de Mecatrnica y Automotizacin

Exmen rpido y puntualidad Trabajo individual (ver rbrica) Cumplimiento del equipo con lo programado (ver rbrica) Reporte (en equipo, excepto donde se indica) o Presentacin y ortografa o Contenido o Conclusiones individuales

20 puntos 10 puntos 10 puntos 10 puntos 30 puntos 20 puntos 100 puntos

Calificacin del laboratorio Promedio de las prcticas Proyectos 75 puntos 25 puntos 100 puntos

Laboratorio de Diseo de Sistemas Lgicos

ITESM

Departamento de Mecatrnica y Automotizacin

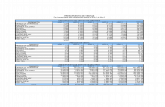

Rbrica para evaluacin de la participacin del alumno en el laboratorio PARMETROS Y CRITERIOS DE EVALUACION Trabajo individual Cumplimiento del equipo con los objetivos programados 0 pts No Trabaja. Se cumpli menos de la mitad de lo programado 6 pts Trabaja pero requiere presin del instructor Se cumpli la mayora de lo programado 10 pts Cumple por iniciativa propia Se cumpli lo programado

Formato de observacin en el laboratorio Grupo InstructorAlumno

____________ ____________Prctica # TI CE Tot. Prctica # TI CE Tot. Prctica # TI CE Tot. Prctica # TI CE Tot. Prctica # TI CE Tot. Prctica # TI CE Tot. Prctica # TI CE Tot. Prctica # TI CE Tot.

Matrcula

Laboratorio de Diseo de Sistemas Lgicos

ITESM

Departamento de Mecatrnica y Automotizacin

PRCTICA #1 COMPUERTAS DIGITALES BSICAS TTLObjetivos: - Uso del protoboard. - Polarizacin de un LED. - Elaborar un detector de seal lgica con un LED. - Generacin de estados lgicos para compuertas digitales. - Obtencin experimental de las tablas de verdad para las compuertas lgicas bsicas: AND, OR y NOT. - Aplicar las compuertas lgicas digitales bsicas en la simulacin de sistemas de control lgico.

DESARROLLO Su instructor describir las partes de un protoboard para ser utilizado en la implantacin de sistemas lgicos digitales. Para ms detalles del protoboard ver anexo A.

Fig. 1: Protoboard

LISTA DE MATERIAL - LEDs - Resistencias de 330 - Dip switch - 7400 - 7402 - 7404 - 7408 - 7432

1) Construir en su protoboard un circuito elctrico, como se muestra en la figura 2, para polarizar adecuadamente un LED (Light Emmiting Diode). Para un mejor funcionamiento de un LED es necesario limitar la corriente If que provoca la luminiscencia del LED. Considere que de acuerdo a datos tcnicos de un LED se tiene que: Vf = 1.5 VCD, e If = 0.015 A. Si el voltaje de polarizacin, Vs = 5 VCD, realice lo siguiente: a) Identifique las terminales nodo y ctodo del LED para realizar una polaridad correcta. b) Calcule el valor de Rs. El valor calculado corresponde a un valor comercial? Explique. c) Observe qu sucede a la intensidad luminosa del LED al utilizar una resistencia de un valor menor o mayor al valor calculado. Explique. d) Vuelva a conectar la resistencia R de mayor valor y mida la cada de voltaje en el LED, Vm, as como el valor de If. Mida el valor del voltaje y su polaridad a travs de la resistencia elctrica del circuito.

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

1

ITESM

Departamento de Mecatrnica y Automotizacin

If

Vs = 5 VCD; Rs = 330 ;

Vf = 1.5 VCD; If = 0.015 A;

Medir: Vm = _________ If = _________

Fig. 2: Circuito de polarizacin para un LED. Fig. 3: Prueba para obtener la tabla de verdad a una compuerta AND, SN74LS08 2) Realice las modificaciones al circuito anterior para que dicho circuito sea utilizado durante su prctica como verificador de voltaje. Compuertas Lgicas Digitales 3) Construya un circuito elctrico en su protoboard para comprobar la tabla de verdad de las compuertas digitales AND, OR y NOT. Consulte la tabla de especificaciones (data sheet, apndice D) para identificar los pines que corresponden a: entradas, salidas y polarizacin (Vcc, Gnd). El circuito debe generar dos entradas de voltaje (1: uno lgico) que debern ser mostrados por dos LEDs, y la salida de la compuerta ser mostrada en otro LED, como se ilustra en la Figura 3. Qu sucede a la salida de las compuertas cuando a las entradas no se conecta voltaje (entradas flotadas)? Explique. 4) Implante la funcin lgica Booleana: F = A.B + A.B utilizando compuertas lgicas bsicas y obtenga su tabla de verdad de manera experimental. Aplicacin 5) El consejo directivo de una empresa se encuentra integrado por tres personas. En una de sus juntas se acord que las votaciones se hicieran de forma secreta; sin embargo, existe el problema de que una persona ajena contara los votos para mantener el secreto del voto. Para evitar este problema se decide hacer lo siguiente: Se instalar un botn debajo de la mesa de cada directivo. Al centro de la sala de juntas se colocarn dos lmparas, una de color roja y una de color verde. Al momento de votar, si el directivo est a favor presionar el botn, si est en contra no lo presionar. La lmpara color verde deber encenderse si la mayora vota a favor. La lmpara de color rojo deber encenderse si la mayora est en contra. a) Elabore la tabla de verdad para obtener la solucin a este problema b) Implante con compuertas lgicas bsicas la solucin encontrada.

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

2

ITESM REPORTE DE LA PRCTICA a) b) c) d) e) f) Breve resumen de la prctica. Descripcin y resultados obtenidos. Esquemas o circuitos que se indiquen Conclusiones (qu aprendi, cmo lo aprendi, qu teora comprob y por qu). Bibliografa Anexar la informacin solicitada por el instructor

Departamento de Mecatrnica y Automotizacin

ANEXOSA) Partes de un protoboard.

Investigar: 1. Una pgina de internet donde estn los datos tcnicos y diagramas de las compuertas digitales bsicas. 2. El funcionamiento y composicin de un LED, incluya especificaciones elctricas.

Fig. 6: Partes de un protoboard. Para la explicacin del protoboard se considera la posicin mostrada en la Fig. 6. Los orificios verticales (columnas) de la zona A estn conectados entre s, al igual que los de la zona B. Existe una ranura que asla los orificios verticales de las zonas A y B. Los orificios horizontales de las zonas A y B estn aislados entre s. Los buses de alimentacin de voltaje corresponden a las barras marcadas con las lneas roja (+) y azul (-). Los orificios se encuentran numerados para facilitar la identificacin de los pines de un chip a ser utilizado.

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

3

ITESM B) Circuito elctrico para generar los niveles lgicos 0 y 1.

Departamento de Mecatrnica y Automotizacin D) Datos para las compuertas lgicas digitales, familia 74XX (data_sheet)

C) Identificacin de los pines de compuertas digitales

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

4

ITESM NOTAS:

Departamento de Mecatrnica y Automotizacin

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

5

ITESM

Departamento de Mecatrnica y Automotizacin

PRCTICA #2 OTROS CIRCUITOS COMBINATORIOS COMUNESObjetivos: - Conocer el uso y funcionamiento del display de 7 segmentos - Conocer el uso y funcionamiento de un decoder - Utilizar el decoder para desplegar nmeros decimales en el display de 7 segmentos - Conocer el uso y funcionamiento de un multiplexor (MUX) - Utilizar el MUX para generar funciones lgicas.

DESARROLLO 1) EL DISPLAY DE 7 SEGMENTOS El display de siete segmentos es un dispositivo de salida en un circuito de control lgico. Este display est conformado por un conjunto de siete LED`s (Light Emitting Diode) acomodados de la siguiente manera:

Led

Fig. 1: Display de siete segmentos Cada uno de los leds o segmentos tienen una letra que los identifica que es la siguiente:A F G E D C B

LISTA DE MATERIAL - LEDs - Resistencias de 330 - Dip switch - Display de 7 segmentos (nodo comn) - Display de 7 segmentos (ctodo comun) - 7447 - 74151

Fig.2: Denominacin de los segmentos Existen dos tipos de display: nodo comn Ctodo comn Los display de nodo comn tienen la siguiente configuracin:

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

1

ITESM5 VDC

Departamento de Mecatrnica y Automotizacin Como se puede observar en la figura, el display de ctodo comn tiene la conexin de tierra como punto comn entre los LEDs.Nota: La lnea continua representa lo que est dentro del dispositivo y la lnea punteada lo que usted debe conectar

Ejercicio1 En el protoboard coloque y compruebe el funcionamiento del display de 7 segmentos de nodo comn. Se sugiere utilizar un resistor de 470 como limitador de corriente. 2) DECODER El decoder es un dispositivo que se encarga de recibir un cdigo y traducirlo a una salida deseada. Este dispositivo puede ser utilizado para traducir el sistema binario (por ejemplo, en formato BCD) y tener una salida en el sistema decimal de la siguiente forma:0 1 2 3 4 5 6 7 8 9

DA05

A

B

C

D

E

F

G

R Seales de activacin (conectar a 0 VDC)

Fig.3: Configuracin nodo comn Como se puede apreciar en la figura todos los LED tienen como punto comn la alimentacin de 5V y debern ser conectados a tierra por medio de un resistor R para limitar la corriente a travs del LED. Los display de ctodo comn tienen la siguiente configuracin:Seales de activacin (conectar a 5 VDC)RA B C D E F G

Sistema binario (en formato BCD)

Ae Be Ce De

Decoder

El estado de las salidas cambiar a un uno lgico dependiendo del cdigo de entrada

Fig.5: Decoder BCD a decimal Por ejemplo este decoder encender la salida 9 si el cdigo de entrada es 1001. A su vez para poder tener un nmero en el display de 7 segmentos se necesitara un circuito combinatorio que recibiera el cdigo binario del nmero que se quiera desplegar y ste lo tradujera a las salidas correctas, para esto se requerira una funcin lgica para cada segmento. Ejercicio 2

DC05

Obtenga la funcin lgica para encender el segmento A en los dgitos del sistema decimal si tuviera un display de 7 segmentos con nodo comn Ejercicio 3

GND

Fig.4: Configuracin ctodo comnLaboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

Obtenga la funcin lgica para encender el segmento A en los dgitos del sistema decimal si tuviera un display de 7 segmentos con ctodo comn2

ITESM Dado que es muy comn requerir este tipo de aplicaciones tambin existen decoders que traducen del sistema binario (en formato BCD) a las seales necesarias para tener un nmero decimal en el display de 7 segmentos. Los decoders ms comunes son: Funcin BCD a Decimal BCD a siete segmentos BCD a siete segmentos Ejercicio 4 Muestre los dgitos en el display de 7 segmentos utilizando el decoder. Enve las seales de entrada conectando y desconectando cables o utilice dip switches 3) MULTIPLEXOR El multiplexor se puede definir como un selector de datos. Este dispositivo tiene varias lneas de entrada y una sola salida, mediante un circuito de control y un cdigo binario se selecciona cual de las entradas se conectar a la salida. Esto se puede observar en el siguiente diagrama:I0 I1 I2

Departamento de Mecatrnica y Automotizacin Se podra obtener la salida del multiplexor por medio de una funcin lgica que dependa del cdigo que entra al circuito de control. Ejercicio 5 Obtenga la funcin lgica de la salida con base en la variables de entrada (Ae, Be, y Ce) y las entradas (I0...I7) (recuerde que la entrada I0 se conectar a la salida cuando tenga el cdigo binario equivalente al cero decimal en las variables de entrada). Afortunadamente no es necesario implantar la funcin lgica porque existen diversos multiplexores comerciales como lo son: Funcin MUX 16 a 1 MUX 8 a 1 MUX 8 a 1 MUX Doble 4 a 1 Tipo 74150 74151 74152 74153 Caractersticas Slo tiene disponible la salida negada Tiene disponible la salida postiva y negada Slo tiene disponible la salida negada Convierte de paralelo a serial

Tipo 7445 7446, 7447, 7449 7448

Caractersticas Salidas de colector abierto Salidas de colector abierto No requiere resistencias externas

Adems de usarlo como selector es comn el usarlo para construir funciones lgicas. Esto se lograra si se coloca la tabla de verdad resultante como entrada al multiplexor e introducimos al circuito de control los valores de las variables que originaron la tabla. Ejercicio 6 El consejo directivo de una empresa se encuentra integrado por tres personas. En una de sus juntas se acord que las votaciones se hicieran de forma secreta; sin embargo, existe el problema de que una persona ajena contara los votos para mantener el secreto del voto. Para evitar este problema se decide hacer lo siguiente: Se instalar un botn debajo de la mesa de cada directivo. Al centro de la sala de juntas se colocarn dos lmparas, una de color roja y una de color verde. Al momento de votar, si el directivo est a favor presionar el botn, si est en contra no lo presionar. La lmpara color verde deber encenderse si la mayora vota a favor. La lmpara de color rojo deber encenderse si la mayora est en contra.3

Valores de uno o cero lgico

I3 I4 I5 I6 I7

Salida

Circuito de controlAe Be Ce

Fig. 6: Funcionamiento de un multiplexorLaboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

ITESM a. Elabore la tabla de verdad para obtener la solucin a este problema b. Implante con un multiplexor la solucin encontrada. Ejercicio 7 (Opcional)

Departamento de Mecatrnica y Automotizacin

ANEXOSA) Identificacin de los pines del display de 7 segmentosG F comn comn A B

Resuelva el ejercicio 6 suponiendo que el consejo directivo se encuentra conformado por 4 personas (A, B, C y D) y que la persona A tiene el voto de calidad en caso de empate. a) Elabore la tabla de verdad para obtener la solucin a este problema b) Implante con un multiplexor la solucin encontrada.

REPORTE DE LA PRCTICA a) b) c) d) Breve resumen de la prctica Descripcin y resultados obtenidos Esquemas o circuitos que se indiquen Conclusiones (qu aprendi, cmo lo aprendi, qu teora comprob y por qu). e) Bibliografa f) Anexar informacin solicitada. Investigar: 1. Las caractersticas (hojas de datos) de al menos un decoder o de un multiplexor que no se mencione en la prctica. 2. Un circuito de aplicacin del multiplexorE D C PD

B) Identificacin de los pines del decoder 7447

Entradas Salidas al display Entradas

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

4

ITESM C) Identificacin de los pines del multiplexor 74151 NOTAS:

Departamento de Mecatrnica y Automotizacin

Entradas Salida Salida negadaHabilitacin (a GND) NOTAS:

Entradas

Cdigo

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

5

ITESM DESARROLLO

Departamento de Mecatrnica y Automotizacin

1) SENSOR FOTOELCTRICO DE BARRERA

PRCTICA #3 OTROS CIRCUITOS COMBINATORIOS COMUNES (PARTE 2)Objetivos: Conocer el uso y funcionamiento interno del sensor fotoelctrico de barrera Aplicar los conocimientos obtenidos en las dos ltimas prcticas en un problema prctico

Uno de los dispositivos ms usado para detectar objetos sin contacto es el sensor fotoelctrico de barrera. Este instrumento ya se utiliz en el Laboratorio de Instrumentacin y Mediciones y en esta prctica tendr la oportunidad de conocer su funcionamiento interno. La configuracin de este sensor es la siguiente. Emisor de Receptor luz infrarroja

LISTA DE MATERIAL - LEDs - Resistencias de 100 - Resistencias de 330 - Dip switch - Sensor fotoelctrico de barrera - Relevador con bobina de 5 V. - Relevador con bobina de 6 V. - Display de 7 segmentos (nodo comn) - 7447 - 74151

Fig. 1: Sensor fotoelctrico de barrera Recuerde que este sensor se basa en la deteccin de luz infrarroja en el receptor. La estructura interna simplificada del sensor se muestra en la siguiente figura:Diodo emisor de luz Fototransistor que funciona como un interruptor activado infrarroja (LED) por la luz infrarroja

5 VDC

A

GND

GND

Fig.2: Estructura interna de un sensor fotoelctrico Nota: Cuando el fototransistor detecta la luz infrarroja la terminal A queda conectada a tierra a travs de la resistencia. Si no detecta la luz infrarroja la terminal queda flotada.Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

1

ITESM Una conexin tpica de este sensor sera:5 VDCDiodo emisor de luz infrarroja (LED)

Departamento de Mecatrnica y Automotizacin

5 VDC R1

Diodo emisor de luz infrarroja (LED)

R2

L (Seal TTL)

5 VDC R1Objeto

GND

GND

Fig.4: Conexin a un circuito TTL del sensor fotoelctricoGND GND

GND

Fig.3: Conexin tpica del sensor fotoelctrico Ejercicio 1 Conecte el circuito que se muestra en la figura 3. Estime R2 para que el LED de salida encienda y apague con la presencia o ausencia de luz. Cuando la seal del sensor fotoelctrico se utilice como entrada de un circuito TTL no es necesario incluir la conexin del circuito de la figura 3 (recuerde que en la prctica anterior se coment que una terminal TTL de entrada que no est conectada se considera como un 1 lgico, es decir, est alimentada con 5 VDC). Por lo anterior el sensor fotoelctrico en un circuito TTL se conectara de la siguiente forma:

Si no hay interferencia el transistor est ACTIVO y la entrada de la compuerta est conectada a 0 VDC (0 lgico) y L=1 Ejercicio 2

Si un objeto interrumpe la luz el transistor est ABIERTO, la entrada a la compuerta est desconectada y es vista como 5 VDC (1 lgico) L = 0

Conecte el circuito que se muestra en la figura 4. Utilice un LED para conocer el estado de la salida L. Note que el emisor trae una letra E en la parte superior, el nodo trae un signo +. 2) TRANSDUCTORES DE POTENCIA En ocasiones es necesario activar una salida de mayor potencia a la proporcionada por una compuerta o circuito TTL. Para realizar esto es necesario un dispositivo que traduzca seales de baja potencia a seales de potencia mayor. Los dispositivos que nos ayudan a realizar la conversin o traduccin de potencia son llamados transductores. Algunos dispositivos que realizan la funcin de transductores son: a) Transistor. Este dispositivo se usa para circuitos con cargas de DC

Seal TTL

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

2

ITESM b) TRIAC. Este dispositivo se usa para circuitos con cargas de AC

Departamento de Mecatrnica y Automotizacin Realice el diseo del circuito de control y constryaloDespliegue del cdigo de la tarjeta

Seal TTL

Tarjeta

c)

Relevador con bobina de 5 VDC. Se usa para circuitos con cargas de cualquier tipo (se debe tener cuidado con la capacidad de corriente del contacto)Cdigo binario Sistema de deteccin del cdigo de tres perforaciones

Circuito CombinatorioPermiso de acceso (TTL)

TransductorBuzzer

Fig.5: Esquemtico del sistema de acceso

GND

Ejercicio 3 En una compaa metalrgica, se desea controlar el acceso a ciertas reas mediante una credencial codificada, pertenecientes a todos los empleados. El cdigo de acceso se grabar en la credencial mediante tres perforaciones. El sistema de control obtendr dicho cdigo revisando mediante sensores fotoelctricos, desplegar el cdigo de la tarjeta que se esta verificando y permitir el acceso activando una indicacin luminosa y un buzzer de 12 VDC. reas a las que se permitir el acceso Gerencia Mantenimiento Ingenieros encargados de hornos Operadores Cdigo 1 4 5 6

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

3

ITESM REPORTE DE LA PRCTICA a) b) c) d) e) f) Breve resumen de la prctica. Descripcin y resultados obtenidos. Esquemas o circuitos que se indiquen Conclusiones (qu aprendi, cmo lo aprendi, qu teora comprob y por qu). Bibliografa Anexar la informacin solicitada por el instructor

Departamento de Mecatrnica y Automotizacin

ANEXOSA) Identificacin de los pines del display de 7 segmentosG F comn comn A B

Investigar: 1. El principio de operacin y un ejemplo de circuito de conexin del TRIAC.

E D

C PD

B) Identificacin de los pines del decoder 7447

Entradas Salidas al display Entradas

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

4

ITESM C) Identificacin de los pines del multiplexor 74151 NOTAS:

Departamento de Mecatrnica y Automotizacin

Entradas Salida Salida negada

Entradas

Cdigo

D) Identificacin de los pines del sensor fotoelctrico

+ + E D

NOTA

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

5

ITESM DESARROLLO 1) LA COMPUERTA NAND

Departamento de Mecatrnica y Automotizacin

PRCTICA #4 SNTESIS DE CIRCUITOS COMBINATORIOS Y CONSTRUCCINCON LGICA ALAMBRADA

La compuerta NAND es una compuerta que equivale a una compuerta AND con su salida negada. El smbolo de esta compuerta y su tabla de verdad son las siguientes: A 0 0 1 1 B 0 1 0 1 F 1 1 1 0

Objetivos: Poner en prctica los conocimientos de sntesis de circuitos combinatorios adquiridos en la clase terica Construir circuitos lgicos combinatorios: Slo con compuertas NAND Con decoders de propsito general A B F

F es 0 slo si A y B son 1

Fig. 1: Compuerta NAND Ejercicio 1

LISTA DE MATERIAL- LEDs

- Resistencias de 330 - Dip switch - 7400 - 7408 - 7432 - 74154

Verifique la tabla de verdad de la compuerta NAND de 2 entradas (7400). Nota: Revise la composicin interna de la compuerta 7410, 7420 y 7430 2) CONSTRUCCIN DE FUNCIONES EXCLUSIVAMENTE CON NAND La compuerta NAND tiene la propiedad que a partir de ella se pueden construir las 3 funciones lgicas bsicas (AND, OR y NOT) y en consecuencia cualquier otra funcin lgica. Por esta razn la compuerta NAND (al igual que la compuerta NOR) se dice que es una compuerta funcionalmente completa. La forma o formas de construir las 3 funciones bsicas se muestran a continuacin: a) Funcin NOT

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

1

ITESM Opcin 1: Entradas puenteadas Ejercicio 2

Departamento de Mecatrnica y Automotizacin

A

FF = A A = A

Construya las 3 funciones bsicas utilizando slo compuertas NAND Cabe mencionar que cuando se va a construir una funcin en forma de suma de productos como:

F = ABC + ABC + DOpcin 2: Una entrada en 1 La funcin, construida con NANDs, quedara:A B C

A 1

FF = A 1 = A

A B C

F

Nota: Recuerde que una entrada no conectada en una compuerta NAND TTL es vista como un 1 lgico, por lo que para fines de prueba puede dejarla desconectada. b) Funcin ANDF

D

Note que se eliminan compuertas NAND al construir la funcin y esto permite utilizar un menor nmero de componentes.

A B

F = A B = A B

Otra forma de construir la funcin sera negando dos veces de la siguiente manera:

c)

Funcin OR

F = ABC + ABC + D F = ABC + ABC + D

A

F

Por lo tanto, si distribuimos la primera negacin la funcin quedara:

B

F = A B = A+ B

F = ( ABC ) (ABC ) D

NAND

Observe que las 3 formas son generalizables a NANDs de n entradasNAND Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles NAND

2

ITESM Observe que la funcin est conformada por varios NAND. Ejercicio 3 Se desea disear un bastn especial para personas invidentes. El bastn deber contar con tres sensores: 1. Un sensor de proximidad N (normal) que detecta la presencia de algn objeto o persona en el cono grande de la figura 2 2. Un sensor de proximidad A (angosto) que detecta la presencia de algn objeto en el cono angosto de la figura 2. 3. Un sensor de proximidad P (pequeo) que detecta la presencia de un objeto en el cono pequeo de la figura 2.

Departamento de Mecatrnica y Automotizacin invidente cuando haya un objeto (o persona) en el cono normal N (el cono ms grande) b) Si el botn B est presionado (usado por el invidente para enfocar) el vibrador deber de vibrar en forma suave cuando haya un objeto en el cono angosto A. c) En cualquier momento que haya un objeto en el cono pequeo P, el vibrador deber vibrar fuerte independientemente de cmo est el botn B. Construya las funciones booleanas utilizando compuertas NAND 3) DECODER DE USO GENERAL Un decodificador de n a 2n es un circuito combinatorio con n entradas y 2n salidas como se muestra en la siguiente en la figura:0 1 2 3 . . 12 13 14 15

NSistema binarioAe Be Ce De

Decoder

A PFig.2: Zonas de sensado del bastn Adems, el bastn contar con: - Un botn pulsador B y - Un vibrador de dos intensidades, para que el bastn avise a la persona la presencia del objeto. El vibrador recibe 2 seales: V (vibrar) y F (vibrar fuerte). Si el vibrador recibe la seal V vibrar. Esta vibracin ser fuerte si la seal de intensidad de vibracin F est activa y suave si no est activa. Obtenga las expresiones booleanas para las seales V y F del vibrador bajo las siguientes consideraciones: a) Si el botn B no est presionado (operacin normal) el vibrador deber vibrar en forma suave, para avisar alLaboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Roblesn= 4 entradas

El estado de las salidas cambiar a un uno lgico dependiendo del cdigo de entrada

2n =24= 16 salidas

Fig.3: Decoder 4 a 16 Para cada codigo binario de entrada se encender (dar un 1 lgico) slo con la salida correspondiente. Ejercicio 4 Obtenga la ecuacin boolena para encender la tres primeras salidas En general, el decoder se puede usar para activar un canal de salida en funcin del codigo binario recibido. En nuestro caso se puede usar para construir funciones lgicas binarias de n variables de entradas.

3

ITESM Si se quisiera implantar la funcin:

Departamento de Mecatrnica y Automotizacin

ANEXOSA) Identificacin de los pines del NAND 7400

F = ABC + ABC + A BC DSe hara de la siguiente manera:0Ae Be Ce De

Sistema binario

Decoder

6 7

F

Fig.4: Implantacin de funciones lgicas con decoders Nota: La entrada A es el bit menos significativo Ejercicio 5 (Opcional) Repita el ejercicio 3 utilizando el decoder 74154 (recuerde que las salidas de este decoder son activo bajo) REPORTE DE LA PRCTICA a) b) c) d) e) f) Breve resumen de la prctica. Descripcin y resultados obtenidos. Esquemas o circuitos que se indiquen Conclusiones (qu aprendi, cmo lo aprendi, qu teora comprob y por qu). Bibliografa Anexar la informacin solicitada por el instructor B) Identificacin de los pines del decoder 74154

Investigar: 1. Como obtener las funciones AND, OR y NOT con la compuerta NOR.

Seales de activacin (a GND)

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

4

ITESM NOTAS: NOTAS:

Departamento de Mecatrnica y Automotizacin

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

5

ITESM DESARROLLO 1) LA COMPUERTA NAND

Departamento de Mecatrnica y Automotizacin

PRCTICA #4 SNTESIS DE CIRCUITOS COMBINATORIOS Y CONSTRUCCINCON LGICA ALAMBRADA

La compuerta NAND es una compuerta que equivale a una compuerta AND con su salida negada. El smbolo de esta compuerta y su tabla de verdad son las siguientes: A 0 0 1 1 B 0 1 0 1 F 1 1 1 0

Objetivos: Poner en prctica los conocimientos de sntesis de circuitos combinatorios adquiridos en la clase terica Construir circuitos lgicos combinatorios: Slo con compuertas NAND Con decoders de propsito general A B F

F es 0 slo si A y B son 1

Fig. 1: Compuerta NAND Ejercicio 1

LISTA DE MATERIAL- LEDs

- Resistencias de 330 - Dip switch - 7400 - 7408 - 7432 - 74154

Verifique la tabla de verdad de la compuerta NAND de 2 entradas (7400). Nota: Revise la composicin interna de la compuerta 7410, 7420 y 7430 2) CONSTRUCCIN DE FUNCIONES EXCLUSIVAMENTE CON NAND La compuerta NAND tiene la propiedad que a partir de ella se pueden construir las 3 funciones lgicas bsicas (AND, OR y NOT) y en consecuencia cualquier otra funcin lgica. Por esta razn la compuerta NAND (al igual que la compuerta NOR) se dice que es una compuerta funcionalmente completa. La forma o formas de construir las 3 funciones bsicas se muestran a continuacin: a) Funcin NOT

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

1

ITESM Opcin 1: Entradas puenteadas Ejercicio 2

Departamento de Mecatrnica y Automotizacin

A

FF = A A = A

Construya las 3 funciones bsicas utilizando slo compuertas NAND Cabe mencionar que cuando se va a construir una funcin en forma de suma de productos como:

F = ABC + ABC + DOpcin 2: Una entrada en 1 La funcin, construida con NANDs, quedara:A B C

A 1

FF = A 1 = A

A B C

F

Nota: Recuerde que una entrada no conectada en una compuerta NAND TTL es vista como un 1 lgico, por lo que para fines de prueba puede dejarla desconectada. b) Funcin ANDF

D

Note que se eliminan compuertas NAND al construir la funcin y esto permite utilizar un menor nmero de componentes.

A B

F = A B = A B

Otra forma de construir la funcin sera negando dos veces de la siguiente manera:

c)

Funcin OR

F = ABC + ABC + D F = ABC + ABC + D

A

F

Por lo tanto, si distribuimos la primera negacin la funcin quedara:

B

F = A B = A+ B

F = ( ABC ) (ABC ) D

NAND

Observe que las 3 formas son generalizables a NANDs de n entradasNAND Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles NAND

2

ITESM Observe que la funcin est conformada por varios NAND. Ejercicio 3 Se desea disear un bastn especial para personas invidentes. El bastn deber contar con tres sensores: 1. Un sensor de proximidad N (normal) que detecta la presencia de algn objeto o persona en el cono grande de la figura 2 2. Un sensor de proximidad A (angosto) que detecta la presencia de algn objeto en el cono angosto de la figura 2. 3. Un sensor de proximidad P (pequeo) que detecta la presencia de un objeto en el cono pequeo de la figura 2.

Departamento de Mecatrnica y Automotizacin invidente cuando haya un objeto (o persona) en el cono normal N (el cono ms grande) b) Si el botn B est presionado (usado por el invidente para enfocar) el vibrador deber de vibrar en forma suave cuando haya un objeto en el cono angosto A. c) En cualquier momento que haya un objeto en el cono pequeo P, el vibrador deber vibrar fuerte independientemente de cmo est el botn B. Construya las funciones booleanas utilizando compuertas NAND 3) DECODER DE USO GENERAL Un decodificador de n a 2n es un circuito combinatorio con n entradas y 2n salidas como se muestra en la siguiente en la figura:0 1 2 3 . . 12 13 14 15

NSistema binarioAe Be Ce De

Decoder

A PFig.2: Zonas de sensado del bastn Adems, el bastn contar con: - Un botn pulsador B y - Un vibrador de dos intensidades, para que el bastn avise a la persona la presencia del objeto. El vibrador recibe 2 seales: V (vibrar) y F (vibrar fuerte). Si el vibrador recibe la seal V vibrar. Esta vibracin ser fuerte si la seal de intensidad de vibracin F est activa y suave si no est activa. Obtenga las expresiones booleanas para las seales V y F del vibrador bajo las siguientes consideraciones: a) Si el botn B no est presionado (operacin normal) el vibrador deber vibrar en forma suave, para avisar alLaboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Roblesn= 4 entradas

El estado de las salidas cambiar a un uno lgico dependiendo del cdigo de entrada

2n =24= 16 salidas

Fig.3: Decoder 4 a 16 Para cada codigo binario de entrada se encender (dar un 1 lgico) slo con la salida correspondiente. Ejercicio 4 Obtenga la ecuacin boolena para encender la tres primeras salidas En general, el decoder se puede usar para activar un canal de salida en funcin del codigo binario recibido. En nuestro caso se puede usar para construir funciones lgicas binarias de n variables de entradas.

3

ITESM Si se quisiera implantar la funcin:

Departamento de Mecatrnica y Automotizacin

ANEXOSA) Identificacin de los pines del NAND 7400

F = ABC + ABC + A BC DSe hara de la siguiente manera:0Ae Be Ce De

Sistema binario

Decoder

6 7

F

Fig.4: Implantacin de funciones lgicas con decoders Nota: La entrada A es el bit menos significativo Ejercicio 5 (Opcional) Repita el ejercicio 3 utilizando el decoder 74154 (recuerde que las salidas de este decoder son activo bajo) REPORTE DE LA PRCTICA a) b) c) d) e) f) Breve resumen de la prctica. Descripcin y resultados obtenidos. Esquemas o circuitos que se indiquen Conclusiones (qu aprendi, cmo lo aprendi, qu teora comprob y por qu). Bibliografa Anexar la informacin solicitada por el instructor B) Identificacin de los pines del decoder 74154

Investigar: 1. Como obtener las funciones AND, OR y NOT con la compuerta NOR.

Seales de activacin (a GND)

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

4

ITESM NOTAS: NOTAS:

Departamento de Mecatrnica y Automotizacin

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

5

ITESM INTRODUCCIN PLD

Departamento de Mecatrnica y Automotizacin

PRCTICA #5 CONSTRUCCIN DE CIRCUITOS COMBINATORIOS CON PLDSObjetivos: Poner en prctica los conocimientos referentes al funcionamiento y uso de los PLD (Programable Logic Devices) Construir circuitos lgicos combinatorios apoyados en la programacin del GAL 16V8

En las prcticas anteriores nos hemos concentrado en la construccin del controlador lgico deseado a partir de la interconexin de componentes estndar (compuertas digitales o circuitos especficos), esto conduce a un circuito con varios chips y una cantidad amplia de conexiones entre ellos. Sin embargo, cuando un controlador lgico va a ser producido en grandes cantidades (reloj digital, juguete, etc) es conveniente disear un circuito integrado especfico para la aplicacin, es decir, un diseo a la medida. Esto reduce el nmero de chips y las conexiones externas pero requiere la participacin del fabricante en el diseo y fabricacin de ste. Una alternativa intermedia, es el uso de dispositivos lgicos programables (PLD por sus siglas en ingles) que si bien son estndares, pueden ser personalizados hasta cierto nivel mediante programacin.

LISTA DE MATERIAL- LEDs

- Resistencias de 330 - Dip switch - Display de 7 segmentos (ctodo comn) - GAL 16V8

La figura muestra una configuracin tpica simplificada de un PLD que permite construir funciones en suma de productos y producto de sumas, tambin se incluyen algunas conexiones como ejemplo.

Fig. 1: Configuracin interna de un PLDLaboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

1

ITESM En la figura se pueden observar los siguientes aspectos: Formacin de trminos producto En la parte superior izquierda estn los pines de entrada. Los valores de las entradas son alimentados en forma normal y complementada mediante las lneas horizontales. Las lneas horizontales de las entradas se cruzan formando una malla con lneas verticales que conectan a funciones AND. Cada compuerta AND formar un trmino producto incluyendo a las entradas (o sus complementos) que hallan sido conectadas a ella. Esta conexin la lleva a cabo el usuario mediante programacin. (ver trmino AB en el ejemplo) Formacin de sumas de productos. En la parte inferior al centro existen varias funciones OR. Cada una formar la suma de los trminos producto que se conecten a ella mediante programacin (ver AB + AC en ejemplo) Seleccin de polaridad de salida La salida de cada OR (suma de productos) es alimentada a una de las terminales de un OR exclusivo (XOR) La otra terminal del XOR puede estar o no conectada a tierra por programacin. Si se conecta a tierra (0 lgico), la salida del XOR ser igual a la del OR y por tanto la suma de productos construida saldr directamente hacia el pin de salida correspondiente (ver la conexin al PIN 1 de la figura) Si no se conecta a tierra (1 lgico), la salida del XOR ser el complemento de la salida del OR (el complemento de la suma de productos) y representar por tanto un producto de sumas, el Teorema de Morgan le permite obtener el producto de sumas correspondiente (ver la funcin AB + AD en la figura 1). Nota: Observe que para tener en producto de sumas una funcin determinada deber introducir las variables negadas. Pines bidireccionales. En la figura, la salida del primer XOR es conectado a un buffer de 3 estados que puede ser o no habilitado por la compuerta AND correspondiente. Si se habilita, la salida del XOR es enviada hacia al pin bidireccional y este funciona como una salida convencional, adems de ser retroalimentado hacia la malla de entrada por si se

Departamento de Mecatrnica y Automotizacin requiere (esto permite obtener resultados parciales que son alimentadas como entradas otra vez). Si no se habilita, el XOR es desconectado del pin bidireccional y este funciona como una entrada ms. Forma de hacer las conexiones. En un PLD de programacin nica, inicialmente todos los puntos de una malla estn conectados mediante fusibles y para lograr la(s) funcin(es) deseada(s) se queman los fusibles de las conexiones no necesarias. El mapa de fusibles a quemar se especifica al quemador mediante un archivo (usualmente .jed). En un PLD reprogramable las conexiones pueden ser habilitadas y deshabilitadas tantas veces como sea necesario. Forma de hacer el mapa de conexiones (.jed) Existen lenguajes de programacin (ABEL: Advanced Boolean Expression Language, CUPL, etc) que permiten especificar el comportamiento deseado del circuito mediante instrucciones. A partir del comportamiento especificado y las caractersticas del PLD el software puede simplificar las funciones y generar el mapa de fusibles. Otros softwares (como el que usaremos en esta prctica) permite dibujar el diagrama lgico, y ste en forma automtica lo traduce a alguno de los lenguajes anteriores para su procesamiento posterior.

Notas: 1. Variedades de PLDs a. A la combinacin de un arreglo AND programable con uno OR programable como el mostrado se le conoce como Arreglo lgico programable mediante campos, (FPLA, por siglas en ingles) o simplemente PLA (Programable Logic Array). b. Cuando el arreglo AND es programable pero el OR es fijo (los ANDs vienen preconectados a los OR por grupos (ejemplo 4 a cada uno) se le conoce como PAL. c. Cuando el arreglo AND es fijo y el OR es programable se les conoce como memorias exclusivas de solo lectura, PROM. d. Recuerde que al construir circuitos secuenciales (no cubiertos en este curso) puede ser necesario que la salida de los OR pasen por memorias (o registros) y retornen a la malla principal. Cuando un dispositivo tambien incluye estas memorias se le conoce como secuenciador lgico programable mediante campos: FPLS o simplemente PLS.

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

2

ITESM FORMAS DE PROGRAMACIN DE UN GAL Existen otras formas de programar las funciones lgicas que se quieran grabar en el GAL. A continuacin se muestran tres formas utilizando como ejemplo el ejercicio 6 de la prctica #2, que plantea lo siguiente: El consejo directivo de una empresa se encuentra integrado por tres personas. En una de sus juntas se acord que las votaciones se hicieran de forma secreta; sin embargo, existe el problema de que una persona ajena contara los votos para mantener el secreto del voto. Para evitar este problema se decide hacer lo siguiente: Se instalar un botn debajo de la mesa de cada directivo. Al centro de la sala de juntas se colocarn dos lmparas, una de color roja y una de color verde. Al momento de votar, si el directivo est a favor presionar el botn, si est en contra no lo presionar. La lmpara color verde deber encenderse si la mayora vota a favor. La lmpara de color rojo deber encenderse si la mayora est en contra. Los 3 pasos bsicos a seguir incluyen: Programacin Compilacin Aplicacin.

Departamento de Mecatrnica y Automotizacin a) Programacin con ecuaciones booleanas utilizando el lenguaje ABEL-HDL Siga los primeros 6 pasos indicados en el anexo A) De la ventana Source-New crear de un nuevo archivo fuente. Seleccione ABEL-HDL Module. La siguiente pantalla aparecer:

La programacin puede resumirse con el siguiente diagrama:Especificaciones del PLD Descripcin del comportamiento Editor de texto o grfico Archivo ABEL Compilador Mapa de fusibles (.jed)

Fig. 3: Pantalla de colocacin de nombres Quemador Diagrama esquemtico de conexiones Chip grabado

Escriba los nombres que se le solicitan y de un click en OK. Aparecer la siguiente pantalla:

Fig. 2: Pasos para programar un PLD

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

3

ITESM

Departamento de Mecatrnica y Automotizacin b) Programacin con tabla de verdad utilizando el lenguaje ABEL-HDL Siga los primeros 6 pasos indicados en el anexo A) De la ventana Source-New crear de un nuevo archivo fuente. Seleccione ABEL-HDL Module. La siguiente pantalla aparecer:

Fig. 4: Pantalla de edicin Introduzca su programa, que para el ejemplo mencionado sera el siguiente:

Fig. 6: Pantalla de colocacin de nombres Escriba los nombres que se le solicitan y de un click en OK. Aparecer la siguiente pantalla:

Fig. 5: Problema resuelto con ecuaciones booleanas Observe que no es necesario tener Title, y observe la nomenclatura para la declaracin de variables y para las funciones lgicas. Posteriormente deber seguir los pasos 12 a 14 descritos en el anexo A) y grabar el GAL conforme al anexo B).4

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

ITESM c)

Departamento de Mecatrnica y Automotizacin Programacin con esquemtico

Los pasos para esta programacin se describen en el anexo A)

Fig. 7: Pantalla de edicin Introduzca su programa, que para el ejemplo mencionado sera el siguiente:

Fig. 9: Problema resuelto con esquemtico

Ejercicio 1 Realice la programacin de un GAL para la solucin del problema de la prctica #2 (planteado al inicio de esta seccin) con cada uno de los tres mtodos de programacin presentados. Fig. 8: Problema resuelto con tabla de verdad Observe que no es necesario tener Title, y observe la nomenclatura para la declaracin de variables y para la tabla de verdad. Posteriormente deber seguir los pasos 12 a 14 descritos en el anexo A) y grabar el GAL conforme al anexo B).5

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

ITESM Ejercicio 2 (opcional) Programar la lgica de control necesaria para controlar un display de 7 segmentos de ctodo comn. 1. 2. 3. 4. 5. Encuentre las ecuaciones Booleanas que resuelven el problema. Simplifique las funciones utilizando el lgebra Booleana Realice un diseo esquemtico de la estrategia de control lgico Grabe en un GAL la lgica de control para el control de los 7 segmentos del display. Comprobar el correcto funcionamiento del circuito utilizando un protoboard y dems elementos requeridos (LEDs, resistencias,...)

Departamento de Mecatrnica y Automotizacin

ANEXOSA) Programacin esquemtica de un GAL utilizando el programa ISP de Lattice A continuacin se describe el procedimiento para utilizar el software ISP: 1. 2. 3. 4. 5. Encender la computadora y esperar hasta que se normalicen los conos en su pantalla. Buscar el cono de ISP System Starter para inicializar el programa. Seleccionar la opcin File-New-Project, como se muestra en la figura A.1. Asignar un nombre al proyecto que no exceda de ocho caracteres. La extensin que identifica a un archivo tipo proyecto ser .SYN. Dar doble click a ispLSI1032E-125LT100 de la ventana Source in Project, como en la figura A.2.

REPORTE DE LA PRCTICA a) b) c) d) e) f) Breve resumen de la prctica. Descripcin y resultados obtenidos. Esquemas o circuitos que se indiquen Conclusiones (qu aprendi, cmo lo aprendi, qu teora comprob y por qu). Bibliografa Anexar la informacin solicitada por el instructor

Investigar: 1. Las caractersticas de los GALs 20V8 y 22V10, incluya las hojas de datos y comente los aspectos ms importantes de stas. 2. Las caractersticas y aplicaciones del PAL y la EEPROM.

Fig. A.1: Pantalla para iniciar un proyecto en ISP

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

6

ITESM

Departamento de Mecatrnica y Automotizacin Elaboracin del diagrama y del archivo esquemtico 8. Definir el nombre del archivo con el que se trabajar y ste ser relacionado con la extensin .sch. La pantalla de captura esquemtica es para definir las compuertas lgicas (AND, OR, NOT,) requeridas para implementar una funcin booleana, como en la figura A.4. Seleccionar el cono de la parte superior izquierda del men Drawing

9.

10. Luego seleccionar la librera denominada GATES.LIB, y dibujar las compuertas requeridas para su proyecto, como se muestra en la figura A.5.

Fig. A.2: Inicializacin de un proyecto 6. 7. Seleccionar (para esta prctica) el GAL16LV8/ZD con empaquetado de 20 pines. Le preguntar si desea cambiar el juego de informacin del dispositivo (change device kits) presionar OK. De la ventana Source-New crear de un nuevo archivo fuente (ver la figura A.3). Seleccione Schematic

Fig. A.4: Herramientas de dibujo (drawing)

Fig. A.3: Seleccin de un archivo fuente

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

7

ITESM Conectores

Departamento de Mecatrnica y Automotizacin

si desea De la caja de herramientas de dibujo (drawing) seleccione el cono realizar una conexin entre compuertas o entre un punto de entrada o salida y una compuerta. Para trazar un conector en lnea recta desde un punto hacia la terminal de un componente se requiere de un clic del ratn para iniciar y otro para terminar el conector. Etiquetas Para obtener las etiquetas seleccione de la caja de herramientas de dibujo (drawing) el cono y aparecer en la parte inferior de la pantalla Net Name Enter Net Name. Escribir el nombre de la variable y posteriormente oprima el ENTER y con el cursor posicione la variable al final del conector deseado y dar un click al ratn. Fig. A.5: Seleccin de compuertas lgicas Puertos de Entrada o Salida . - Seleccionar de la caja de herramientas de dibujo (drawing) el cono Aparecer un men de opciones titulado I/O en donde debe elegir el tipo de puerto a usarse ( None, Input, Ouput y Bidirection), como en la figura A.7.

Fig. A.7: Asignacin de puertos de entrada/salida a una compuerta lgica.

Fig. A.6: Seleccin de las compuertas requeridas

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

8

ITESM

Departamento de Mecatrnica y Automotizacin Link Design Aqu verifica si el o los archivos contienen un cdigo vlido , en caso de que no sea aceptado aparecer un mensaje que incluye una explicacin y un cdigo de error. Fit Design En algunas ocasiones los requerimientos de nuestro diseo sobrepasan la capacidad del dispositivo seleccionado. Esta rutina verifica si el diseo cabe en el dispositivo seleccionado, en caso de que no sea lo suficientemente se sugiere seleccionar un dispositivo de mayor capacidad como el GAL20V8 o el GAL22V10. Create Fuse Map En este proceso se obtienen dos archivos: El archivo reporte con extensin .rep que contiene la informacin de las ecuaciones, la distribucin de terminales PIN OUT, el porcentaje de utilizacin del dispositivo , etc. En el archivo .rep (Chip report) se presenta la lgica que ha sido generada as como un PINOUT del GAL programado. Un ejemplo de esto se muestra en la figura A.9 y en la figura A.10. Consultar el archivo schematic.report para observar la asignacin de las entradas y salidas dentro del GAL, como en la figura A.9 y en la figura A.10.

Fig. A.8: Esquemtico terminado. Se puede observar que en la figura A.8 se muestra el ejemplo de un diagrama esquemtico completo, que incluye las compuertas AND, OR, NOR y NAND. Se debe guardar el archivo esquemtico y se debe continuar con la creacin del programa a grabar en el GAL siguiendo el siguiente proceso: 11. Regresar a la ventana de ISP System Starter y asegurarse de la presencia en el recuadro izquierdo (Sources in Project igual al del dispositivo definido (GAL16V8ZD), y en el mismo recuadro la presencia del archivo con extensin .SCH 12. Iniciar el proceso de compilacin ejecutando las siguientes rutinas que aparecern en el recuadro derecho ( Processes for Current Source). 13. Dar doble click al archivo creado, y ejecutar las funciones: Compile, Check, and Reduce. Si no hubo problemas aparecer una paloma en color verde. 14. Posicionarse en GAL 16LV8/ZD y ejecutar las funciones: Link, Fit, y Create Fuse. El significado de cada funcin se explica a continuacin: Update all schematic Files En esta parte del proceso se actualizan los archivos que sern tomados en cuenta para la compilacin (no ejecutar para esta prctica).Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

9

ITESM

Departamento de Mecatrnica y Automotizacin B) Procedimiento para grabar el programa en el GAL Una vez generados los archivos anteriores proceder a grabar el programa en el GAL. Para esto de debe utilizar el programador universal que se encuentra conectado al puerto paralelo de la PC, como se muestra en la Fig. B.1.

Fig. A.9: Vista del archivo reporte.

Fig. B.1: Programador Universal conectado a un sistema PC. La secuencia de programacin es la siguiente : 1. 2. 3. Acceder al archivo ejecutable del programa de grabacin. (CHIPMAX for Windows). Aparecer la pantalla de la aplicacin como se muestra en figura B.2. Seleccionar el dispositivo a programar (LATTICE GAL16V8D). Cargar el archivo JEDEC que previamente fue diseado utilizando la opcin FILE-LOAD.

Fig. A.10: Vista de la asignacin de entradas y salidas programadas en el GAL (PINOUT)

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

10

ITESM

Departamento de Mecatrnica y Automotizacin

Fig. B.3: Seleccin del archivo ejecutable Fig. B.2: Pantalla del men del programa del programador CHIPMAX. 4. 5. 6. 7. Colocar el GAL en la base del programador y sujetarlo con la palanca. Borrar el contenido previo del GAL seleccionando el cono ERASE. Al terminar de borrarse el estado indicar OK, si es que se puede proseguir. Verificar el estado de limpieza del GAL con BLANK. Nuevamente si la operacin es correcta aparecer el estado OK. Seleccionar el cono PROG.

Si aparece un mensaje de que la tarea de programacin se realiz con xito entonces el dispositivo estar listo para probarse. Se puede verificar que el grabado se realiz correctamente utilizando el cono Verify.

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

11

ITESM C) Configuracin del display de siete segmentos de ctodo comnSeales de activacin (conectar a 5 VDC)RA B C D E F G

Departamento de Mecatrnica y Automotizacin D) Hojas de especificaciones del GAL 16V8

DC05

GND

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

12

ITESM

Departamento de Mecatrnica y Automotizacin

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

13

ITESM

Departamento de Mecatrnica y Automotizacin

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

14

ITESM NOTAS: NOTAS:

Departamento de Mecatrnica y Automotizacin

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

15

ITESM INTRODUCCIN

Departamento de Mecatrnica y Automotizacin

PRCTICA #6 MEMORIAS Y FLIP-FLOPSObjetivos: Conocer la diferencia entre control lgico secuencial y control lgico combinatorio Conocer las memorias, su construccin y los circuitos integrados que realizan esta funcin Conocer las memorias, su construccin y los circuitos integrados que realizan esta funcin

Hasta este momento, en las prcticas anteriores se ha trabajado con circuitos lgicos combinatorios; es decir, circuitos que para cada combinacin de entradas el circuito dar siempre la misma combinacin de salidas. La propiedad antes mencionada permite que el comportamiento de los circuitos lgicos combinatorios pueda ser descrito completamente con una tabla de verdad.Entradas

Circuito Combinatorio

Salidas

Fig. 1: Configuracin de un circuito combinatorio Hay otro tipo de circuitos en los cuales para una misma combinacin de entradas pueden existir diferentes combinaciones de salidas en diferentes momentos. La razn de lo anterior es que ese tipo de circuitos va pasando por diferentes estados a travs del tiempo y la salida, en un momento dado, depende de la combinacin de entradas y del estado actual. A este tipo de circuitos se les conoce como circuitos secuenciales. Los circuitos secuenciales para poder generar las salidas deseadas o correctas deben tener la capacidad de recordar el estado actual y cambiarlo en los momentos adecuados.Entradas Salidas

LISTA DE MATERIAL- LEDs

- Resistencias de 330 - Dip switch - 7400 - 7402 - 7404 - 7408 - 7432 - 7474 - 74107A - 74249

Circuito Combinatorio

Informacin sobre el estado actual

Elementos de memoria

Seal para cambiar de estado

Fig. 2: Configuracin de un circuito secuencial Existen varios dispositivos de memoria como los contadores, secuenciadores, etc; todos ellos estn formados y pueden ser construidos con elementos de memoria bsicos que se conocern en esta prctica.

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

1

ITESM MEMORIA SET-RESET Una de las memorias de mayor aplicacin es la memoria SET-RESET (latch SET-RESET).S Q

Departamento de Mecatrnica y Automotizacin Existen varias formas de construir esta memoria como: 1) Construccin con base en compuertas bsicas Para construir esta memoria con compuertas bsicas es necesario conocer la funcin lgica que la describe. La funcin se obtiene a partir de una tabla de verdad con las definiciones a), b) y c) mencionadas en la seccin anterior. S 0 0 1 1 R 0 1 0 1 Q Q 0 1 nPara poder generar la salida necesita saber el valor actual de ella misma

R Fig. 3: Esquema de una memoria SET-RESET

Esta memoria tiene las siguientes caractersticas: a) Se activa (prende la salida Q) cuando recibe un pulso en la seal S (SET) b) Se desactiva (apaga la salida Q) cuando recibe un pulso en la seal R (RESET) c) Si no recibe ninguna de las dos seales (ni S ni R) mantiene su estado actual En la figura 4 se muestra un diagrama de tiempos del funcionamiento de esta memoria.

Debido a la situacin mostrada en la tabla de verdad se construye una nueva tabla de verdad de la siguiente forma: S 0 0 0 0 1 1 1 1 R 0 0 1 1 0 0 1 1 Qactual 0 1 0 1 0 1 0 1 Q 0 1 0 0 1 1 n n

S R QFig. 4: Diagrama de tiempos de una memoria SET-RESET Nota: Si se activan simultneamente la seal SET y la seal RESET la salida depender del tipo de construccin interna de la memoria e incluso puede llegar a tener una salida inestable, por lo cual no se recomienda activar al mismo tiempo la seal SET y la seal RESET.

Construyendo el mapa de Karnaugh tenemos:S

R

0 1 0 0

1 1 n n

Qactual

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

2

ITESM En suma de productos la funcin sera: 2)

Departamento de Mecatrnica y Automotizacin Construccin con base en NORs La funcin lgica en formato de NOR se obtiene de la siguiente manera:

Q = S + QRS

R

0 1 0 0

1 1 n n

Q = (S + Q )R = (S + Q )R = R + (S + Q )Qactual

Por lo que el diagrama es:

En producto de sumas la funcin sera:

Q = (S + Q )R- En la primera ecuacin en caso de presentarse la seal de SET RESET simultneos la salida Q se enciende. - En la segunda ecuacin en caso de presentarse la seal de SET y RESET simultneos la salida Q se apaga. Esto es deseable en muchas aplicaciones reales y se usar mucho esta ecuacin por lo que se le pide que la MEMORICE. El diagrama de la funcin en producto de sumas con compuertas bsicas es el siguiente:

S R

Q

Fig. 6: Diagrama de una memoria SET-RESET con NORs Tambin puede requerirse Q y Q , para esto el diagrama es de la siguiente forma:

S

Q

S R

Q

R

Q

Fig. 5: Diagrama de una memoria SET-RESET Ejercicio 1 Construya la memoria SET-RESET con compuertas bsicas y verifique su comportamiento conectando la salida a un LED. Ejercicio 2

Fig. 7: Diagrama de una memoria SET-RESET con NORs

Construya la memoria SET-RESET con NORs para obtener Q y Q Verifique su comportamiento conectando las salidas a un LED.

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

3

ITESM 3) Construccin con base en NANDs El circuito para tener Q y Q con NAND`s es:

Departamento de Mecatrnica y Automotizacin

Entradas

Circuito Combinatorio

Salidas

S

Q

Informacin sobre el estado actual

Elementos de memoria

Seal para cambiar de estado

Reloj (clock)

R4) El circuito 74279

Q

Fig. 9: Configuracin del circuito secuencial con reloj (clock) La seal de reloj (clock) se activar para permitir el cambio de estado, luego se desactivar durante un periodo de tiempo pequeo (para permitir la estabilizacin del circuito combinatorio) y se activar nuevamente repitiendo el ciclo en forma indefinida Un circuito de memoria SET-RESET que se actualiza slo cuando est activa la seal de reloj es:S Q C Q R

Fig. 8: Diagrama de una memoria SET-RESET con NANDs

Este circuito incluye cuatro memorias SET-RESET con entradas activas bajas (es decir, como la figura 8 pero sin los negadores). Para activarlas se debe hacer S=0 y para desactivarlas R=0. Ejercicio 3 Verifique el comportamiento del circuito 74279 conectando la(s) salida(s) a un LED. MEMORIAS CON RETRASO Al disear circuitos secuenciales pueden existir problemas de carreras crticas. Observe en la figura 2 que al momento de cambiar de estado, si varias seales de la informacin del estado actual deben cambiar a la vez (por ejemplo, de estado 00 a 11), las seales de cambio al propagarse por la red combinatoria llegarn con retrasos diferentes (quiz por nanosegundos, pero diferentes) provocando que durante un pequeo intervalo de tiempo aparezca una informacin de estado errnea (por ejemplo 01 10). Este estado errneo puede disparar a su vez otros estados que alteren el comportamiento deseado del circuito o incluso que lo hagan inestable. Para evitar esto sera deseable que las memorias slo ejecutaran los cambios de estado despus de que las seales de la red combinatoria se hubiesen estabilizado. Para esto se podra usar un esquema como el siguiente:Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

Fig. 10: Diagrama de una memoria SET-RESET con retardo Observe que si la seal de C (clock) est en 0 la memoria SET-RESET no cambiar independientemente de los valores de S y R. Cuando C=1 las seales S y R podrn pasar. Este arreglo se conoce como una memoria SET-RESET con retardo (Observe que ahora S y R si son entradas activas altas). En ocasiones slo se desea retrasar una seal hasta que el reloj lo permita. Para esto la memoria de la figura 9 se debe conectar de la siguiente manera:4

ITESMD Q C Q

Departamento de Mecatrnica y Automotizacin FLIP-FLOPs MS COMUNES a) FLIP FLOP D (Delay) El flip-flop D es muy utilizado en el almacenamiento de datos, ya que posee la caracterstica de retener el dato que recibe de entrada almacenndolo hasta que ste cambie de estado. El nombre de este flipflop proviene del retraso que sufre la seal de entrada (D, delay) D 0 1 Q 0 1

Fig. 11: Diagrama de una memoria D Este arreglo es conocido como memoria D (Delay) con retraso y est disponible en el circuito TTL 7475. MEMORIAS SNCRONAS (FLIP-FLOPs) La restriccin del cambio de estado por nivel de reloj, comentado en el apartado anterior, requerira que el pulso de reloj dure lo suficiente para que cambie la memoria una vez, pero que no fuera tan largo como para que el circuito combinatorio alcance a reaccionar de nuevo, lo cual es difcil de obtener. Para resolver este problema se han diseado arreglos de memorias (conocidas como memorias sncronas o Flip-Flops) que para ejecutar cada cambio de su salida requieren alguna de las siguientes condiciones: FLIP-FLOP disparado por pulso. En este tipo de arreglos, cuando el reloj est en el valor alto, se reciben entradas, pero la salida se cambia hasta que el reloj est en el valor bajo; es decir, se requiere el pulso completo (ascenso y descenso de la seal de reloj) para ejecutar un cambio de estado, pero ya no hay riesgo alguno de inestabilidad. FLIP-FLOP disparado por transicin positiva. En este tipo de arreglos al momento de la transicin positiva se leen las entrads y se ejecuta el cambio de estado una sola vez. FLIP-FLOP disparado por transicin negativa. En este tipo de arreglos al momento de la transicin negativa se leen las entradas y se ejecuta el cambio de estado una sola vez.

DC

Q Q

Fig. 12: Diagrama y tabla de verdad de un flip-flop D El circuito 7474 es una memoria D activada por flanco positivo y con dos seales ms que se conocen como preset y clear, donde el preset mantiene en 1 la salida independientemente de lo que pase en la entrada, mientras el clear mantiene en 0 la salida independientemente de la entrada. Ejercicio 4 Verifique el comportamiento del flip-flop D 7474 conectando la(s) salida(s) a un LED. b) FLIP-FLOP T El flip-flop T se utiliza con frecuencia en la elaboracin de mdulos contadores, la funcin de este dispositivo consiste en cambiar su estado actual al opuesto (inverso), con base en una transicin negativa en la entrada T. El nombre de este flip-flop proviene del disparo o alternacia que sufre la seal (T-Trigger o Toggle) T 0 1 Q

Q Q

TC

Q

Fig. 13: Diagrama y tabla de verdad de un flip-flop TLaboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles 5

ITESM c) FLIP-FLOP JK El flip-flop JK es uno de los ms utilizados en la elaboracin de circuitos lgicos secuenciales, y es bsicamente una extensin del flip-flop SR, la nica diferencia radica en que la combinacin de entrada J=K=1, que en la memoria SR no est permitida, aqu se manda de salida el estado de memoria Q negada. J K Q 0 0 Q 0 1 1 1 0 1 0 1

Departamento de Mecatrnica y AutomotizacinD

JC

Q Q

K

Fig. 16: Diagrama de un flip-flop JK usado como D Para obtener un flip-flop T utilizando JKs se debe conectar la misma entrada T a ambas entradas de la memoria JK como se muestra en la figura.T

Q

JC

Q Q

Fig. 14: Tabla de verdad de un flip-flop JK Una de las grandes ventajas del flip-flop JK es que con ste se pueden construir los tres flip-flops ms comunes mencionados anteriormente como lo son el SR, D y T. Como se dijo, la construccin del flip-flop SR con el flip-flop JK slo debe ignorarse la salida de la combinacin de entrada no permitida en el flip-flop SR, ya que las salidas en las dems combinaciones son las mismas.S

KEjercicio 5

Fig. 17: Diagrama de un flip-flop JK usado como T

Verifique el comportamiento del flip-flop JK 74107A conectando la(s) salida(s) a un LED. Ejercicio 6

JC

Q Q

Realice los flip-flops SS, D y T utilizando el flip-flop JK 74107A Ejercicio 7 (opcional) Se desea controlar el arranque y paro de una bomba que suministra agua a una cisterna que se vaca constantemente. La bomba deber arrancar cuando el nivel del agua se encuentre por debajo del electrodo de nivel bajo B, y deber detenerse cuando el nivel del agua alcance al electrodo de nivel alto A. Los electrodos de nivel, tomarn el estado lgico uno cuando entren en contacto con el nivel del agua.

R

K

Fig. 15: Diagrama de un flip-flop JK usado como SR La construccin del flip-flop D con JKs se realiza conectando la entrada a J directamente, y la entrada K debe ser el inverso de la entrada J, esto se puede realizar simplemente utilizando un inversor como se muestra en la figura.

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

6

ITESM REPORTE DE LA PRCTICA a) b) c) d) e) f) Breve resumen de la prctica. Descripcin y resultados obtenidos. Esquemas o circuitos que se indiquen Conclusiones (qu aprendi, cmo lo aprendi, qu teora comprob y por qu). Bibliografa Anexar la informacin solicitada por el instructor

Departamento de Mecatrnica y Automotizacin

ANEXOSA) Identificacin de los pines del OR 7432

Investigar: 1. Una aplicacin de cada uno de los FFs SR, JK, D y T

B) Identificacin de los pines del AND 7408

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

7

ITESM C) Identificacin de los pines del NOR 7402

Departamento de Mecatrnica y Automotizacin

D) Identificacin de los pines de la memoria S-R 74279

E) Identificacin de los pines de la memoria D 7474

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

8

ITESM F) Identificacin de los pines de la memoria J-K 74107A NOTAS:

Departamento de Mecatrnica y Automotizacin

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

9

ITESM INTRODUCCIN

Departamento de Mecatrnica y Automotizacin

PRCTICA #7 CIRCUITOS DE TIEMPOY OTROS CIRCUITOS SECUENCIALES COMUNES

En la prctica anterior, se entendi la necesidad de utilizar una seal de reloj que sincronice el cambio de estado de los dispositivos de memoria en los circuitos secuenciales.Entradas Salidas

Objetivos: Conocer el circuito LM555 y sus diferentes usos Conocer los circuitos de corrimiento de registros Conocer los contadores sncronosInformacin sobre el estado actual

Circuito Combinatorio

Elementos de memoria

Seal para cambiar de estado

Reloj (clock)T

Fig. 1: Configuracin del circuito secuencial con reloj (clock) LISTA DE MATERIAL- LEDs

- Resistencias de 100 - Resistencias de 330 - Resistencias de 1000 - Capacitores de 1 F - Capacitores de 100 F - Capacitores de 1000 F - LM 555 - 7474 - 74163A

En la figura 1, el periodo T debe ser lo suficientemente grande para que el circuito combinatorio estabilice sus salidas entre cada instante de actualizacin. En los siguientes apartados se mostrar como generar esta y otras seales de tiempo. CIRCUITOS DE TIEMPO Mdulo temporizador 555 Este mdulo consiste de una memoria SET-RESET disparada por las seales de salida de dos comparadores anlogos, como se muestra en la figura 2.

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

1

ITESMVcc Reset

Departamento de Mecatrnica y Automotizacin Ejercicio 1La memoria se apaga (RESET) cuando: Vthreshold > 2/3Vcc La memoria se prende (SET) cuando: Vtrigger < 1/3VccUmbral (threshold) + -

R0 R S Q QDescarga Cada vez que la memoria se apaga la descarga se conecta a tierra. Salida

+ Disparador (trigger)

Conecte el circuito 555 como temporizador de un pulso (one shot). Verifique el funcionamiento de las dos opciones de conexin de salida con un LED y enve la seal de entrada con un interruptor. Nota: Se sugiere un pulso de alrededor de 6 segundos. Se sabe que

t 1.1Ra C

GND

Conexin para generar un pulso peridico de reloj (multivibrador aestable) La estrategia bsica para conectar el circuito 555 como un generador peridico de pulsos es utilizar la seal de salida y la descarga para cargar y descargar un circuito RC. El voltaje variable del capacitor es introducido a los comparadores por medio del umbral y el disparador, generando alternativamente seales de SET y RESET.Vcc

Fig. 2: Configuracin del temporizador 555 Conexin como temporizador de un pulso (one shot) Esta configuracin permite generar un pulso de salida con duracin fija cada vez que se recibe una seal de disparo.Disparo

SalidaUmbral (threshold)

R0 R S Q QSalida RA

t

Fig. 3: Diagrama de tiempos del temporizador 555 como one shot La duracin del pulso de salida es ajustable mediante un circuito RC (resistor-capacitor).

+ -

+ Disparador (trigger)

C

GND

Entrada o disparo

Salida

Entrada o disparo

Salida

RB

Fig. 5: Conexin del temporizador 555 como multivibrador aestable

Fig. 4: Conexin del temporizador 555 como one shotLaboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles 2

ITESM REGISTRO DE CORRIMIENTO Inicio. El voltaje del capacitor Vc =0, por lo que se dispara el SET, Q se activa y el capacitor se carga a travs de RA y RB. b) Estado 1. Cuando Vc > 2/3 Vcc, entonces el RESET se dispara, Q a) se desactiva y Q conecta la terminal de descarga a tierra. El capacitor se descarga a travs de RB. Estado 2. Cuando Vc < 1/3 Vcc, se dispara el SET, Q se activa y el capacitor se carga de nuevo.

Departamento de Mecatrnica y Automotizacin

c)

El circuito OSCILAR entre los estados 1 y 2. Podemos saber el tiempo del pulso generado por este circuito analizando los circuitos RC que se forman en los diferentes estados de funcionamiento. Por lo que:

El registro de corrimiento consiste en un dispositivo que almacena n bits de informacin binaria y retarda n pulsos de reloj la salida de un bit determinado. El nmero n depende de las compuertas que se utilicen para realizar el arreglo o del dispositivo comercial que se use. El registro de corrimiento tiene varios arreglos como paralelo-paralelo, paraleloserial y serial-serial que es el que utilizaremos en esta prctica. El registro de corrimiento se puede construir con un arreglo de memorias D, cabe recordar que la memoria D se puede realizar con un memoria S-R o J-K. El funcionamiento del registro de corrimiento serial-serial se muestra de manera esquemtica en la figura 6.

thigh = 0.693(RA + RB )C tlow = 0.693RBC T = thigh + tlow T = 0.693(RA + 2 RB )C

1Entrada

0 1 0 0 1 0

0Salida

1 0 1 0 0 1

1Salida

Despus del pulso de reloj la informacin se recorre un bit

TSalida Vc 2/3 Vcc 1/3 Vcc

Fig. 6: Diagrama del funcionamiento de registro de corrimiento El arreglo con memorias D se muestra en la figura 7.Entrada

D

Q

D

Q

D

Q

Salida

Reloj

Fig. 7: Diagrama del funcionamiento de registro de corrimiento Fig. 6: Diagrama de tiempos del temporizador 555 como multivibrador aestable Ejercicio 2 Conecte el circuito 555 como multivibrador aestable. Verifique el funcionamiento de la salida con un LED. Nota: Se sugiere un pulso de alrededor de 0.2 segundos. Las resistencias debern ser mayores a 1kLaboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

Ejercicio 3 Construya un registro de corrimiento de al menos 4 bits con el circuito 7474. Verifique el funcionamiento de cada etapa y de la salida con un LED. Nota: Como reloj utilice el pulso del circuito de tiempo armado en el ejercicio 2.

3

ITESM CONTADOR Existen circuitos comerciales que tienen las funciones de contador tal como el 74160, el 74162 el 74163A. En esta prctica se utilizar el circuito 74163A que es un contador binario sincrnico de 4 bits que cuenta los pulsos de reloj. Este contador tiene las siguientes caractersticas: Clear asncrono: Esta entrada al circuito hace la cuenta cero y domina sobre todas las dems entradas. Note que el contador puede trabajar con lgica negativa, es decir, se habilita con 0 lgico. Load sncrono: Al instante del pulso de reloj posiciona la cuenta en el valor dado por las entradas ABCD. RCO (Ripple Carry Out): Este punto da una salida de 1 lgico cada vez que la cuenta llegue al final. Enable T: Detiene la cuenta y deshabilita la salida RCO. Enable P: Detiene la cuenta Ejercicio 4 Verifique el funcionamiento del contador 74163A colocando LEDs a la salida y en el RCO. Verifique el funcionamiento del clear, load, enable T y enable P. Nota: Como reloj utilice el pulso del circuito de tiempo armado en el ejercicio 2. REPORTE DE LA PRCTICA a) b) c) d) e) f)

Departamento de Mecatrnica y Automotizacin

Breve resumen de la prctica. Descripcin y resultados obtenidos. Esquemas o circuitos que se indiquen Conclusiones (qu aprendi, cmo lo aprendi, qu teora comprob y por qu). Bibliografa Anexar la informacin solicitada por el instructor

Investigar: 1. El funcionamiento de los multivibradores monoestables como circuitos de tiempo. Incluir un ejemplo de uno de stos.

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

4

ITESM

Departamento de Mecatrnica y Automotizacin C) Identificacin de los pines de l contador 74163A

ANEXOSA) Identificacin de los pines del circuito 555

B) Identificacin de los pines de la memoria D 7474

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

5

ITESM NOTAS: NOTAS:

Departamento de Mecatrnica y Automotizacin

Laboratorio de Diseo de Sistemas Lgicos Dr. Jorge Limn Robles

6

ITESM

Departamento de Mecatrnica y Automotizacin CONTADOR DE PULSOS DE RELOJ a) Diseo intuitivo de un contador de pulsos de reloj asncrono con flip flop JK Observe la siguiente numeracin binaria para tres variables de salida: Q2 0 0 0 0 1 1 1 1 Q1 0 0 1 1 0 0 1 1 Q0 0 1 0 1 0 1 0 1

PRCTICA #8 APLICACIONES DE FLIP FLOPSObjetivos: Conocer el funcionamiento y la construccin de un contador asncrono y sncrono utilizando flip flops JK Construir un contador de eventos Aplicar los conocimientos de circuitos de tiempo y de flip flops en un problema prctico

LISTA DE MATERIAL- LEDs