SISTEMES ELECTRÒNICS DIGITALS -...

Click here to load reader

Transcript of SISTEMES ELECTRÒNICS DIGITALS -...

EX3: Application project 1: A real-time clock in CPLD or FPGA using VHDL

EX3 de Sistemes Electrònics Digitals

GRUP:

DATA:

Descripció de les aportacions realitzades i de les conclusions d’aquest exercici

TEMPS D’ESTUDI I DE PREPARACIÓ DE L’EXERCICI:

Sessions TGA a l’aula:Sessions TGB al laboratori Sessions TGC fora de l’horari Treball individual Estudiant 1: Estudiant 2: Estudiant 3: Mitjana de temps total (per estudiant)

ÍNDEX DE CONTINGUT

Application project 1: Real-time clock in CPLD or FPGA using VHDL...............................................3

1.1 Description.....................................................................................................................................3

1.2 Objectives......................................................................................................................................3

1.3 Study time:.....................................................................................................................................3

1.4 Designing the 16-key keypad scanning decoder............................................................................41.4.1 Keypad characteristics and wiring........................................................................................41.4.2 Plan the state diagram for the component.............................................................................41.4.3 Synthesize and integrate the component into a new top-level Quartus-II project.................4

1.5 Designing the multiplexed 7-segment display system...................................................................5

1.6 Designing the real time clock control unit (CU)............................................................................51.6.1 State diagram.........................................................................................................................51.6.2 Synthesis and implementation................................................................................................5

1.7 Improvements and new features....................................................................................................5

1.8 Desenvolupament de la pràctica/problema. Treball del grup (títol 2)...........................................61.8.1 El vostre primer subtítol (títol 3)...........................................................................................6

1

Aquest apartat és obligatori. Si no és present, no es corregeix l’exercici i s’ha de tornar a lliurar

Heu d’apuntar tot el temps d’estudi que heu dedicat a l’exercici

EPSC – SED: Sistemes Electrònics Digitals

1.9 Bibliografia i referències consultades............................................................................................6

1.10 Pla de treball que heu preparat per resoldre el disseny..................................................................7

1.11 “Fulls de dubtes” de l’EX2............................................................................................................81.11.1 Sobre els apartats A), B) i C) de disseny del codificador del teclat hexadecimal.................81.11.2 Sobre l’apartat D) de disseny del multiplexor de displays....................................................81.11.3 Full de dubtes sobre els apartats E) i F) de la unitat de control.............................................9

MOLT IMPORTANT: Aquest curs s’espera de vosaltres que ja prepareu i editeu textos de certa qualitat, per tant: preneu aquest document de plantilla d’estils i formats. Amplieu-lo i modifiqueu-lo per plantejar, desenvolupar, solucionar i verificar el funcionament del vostre disseny. NO ES POT LLIURAR CAP TREBALL QUE NO SEGUEIX EXACTAMENT AQUESTA PLANTILLA:

- Fixeu-vos que l’índex de contingut de l’exercici es genera automàticament si respecteu els estils: Normal, Títol 1, Títol 2 i Títol 3.

- Respecteu i useu l’estil del peu de figura (Llegenda) i les referències creuades a les figures que s’actualitzen automàticament quan n’inseriu de noves.

- Respecteu i useu les referències creuades a la bibliografia numerada - Passeu el corrector ortogràfic i repasseu la gramàtica tant si escriviu en anglès, castellà o català.- Per eliminar errors, feu una segona lectura a través dels companys de grup abans de lliurar l’exercici

Consulteu-nos també qualsevol dubte que tingueu sobre l’edició de documents i aquesta plantilla en particular. Tingueu en compte les anotacions i indicacions que us han fet els professors en els vostres treballs previs, per tal de no cometre les mateixes errades en aquest treball

ACTIVITATSQui Què Com QuanGrup de treball cooperatiu Edició impresa (primera

versió) de l’informe de l’exercici. Imprimiu la pàgina 1 i 2 amb l’índex actualitzat 1 i a partir de la pàgina 6

Amb la plantilla i seguint el documents de criteris de qualitat

Abans de la data límit que trobareu al pla de treball o bé al tauló d’anuncis de la web de SED

Els professors o els companys a través d’una correcció creuada

Correcció de la primera versió

Amb la plantilla d’avaluació

Com a màxim una setmana desprès del lliurament de la primera versió impresa

(amb caràcter voluntari)2

Grup de treball cooperatiu Edició electrònica (segona versió) del document complet amb la incorporació de les millores assenyalades pels correctors

Amb un generador de fitxers PDF

Com a màxim una setmana desprès del lliurament de la correcció. S’enviarà per correu electrònic als professors.

Professors Penjar a la web de SED el document per evidenciar el treball desenvolupat

A través d’un enllaç al document a l’apartat de Grups de Classe

Durant el quadrimestre, si s’escau

NOTA: També es valora la iniciativa. Si el grup cooperatiu vol realitzar una aplicació similar a la presentada en aquest exercici que incorpori els conceptes introduïts, bàsicament el disseny d’un altre sistema digital combinacional amb VHDL, que ho comuniqui als professors i es considerarà.

1 Recordeu que l’índex de continguts el genera automàticament el processador de textos 2 És clar que la realització d’aquesta feina addicional millora la qualificació de l’exercici

2

EX3: Application project 1: A real-time clock in CPLD or FPGA using VHDL

Application project 1: A real-time clock in CPLD or FPGA using VHDL

1.1 DescriptionThis exercise will integrate the work developed in previous exercises: display decoders and operational unit (OU), and, furthermore, add the circuitry necessary to control the complete system from a 16-key keypad as described in the initial project from ED3.

Firstly, a scanning keyboard decoder will be implemented, studying the way a 16-key matrix keypad works, and proposing the finite state machine (FSM) that will produce the corresponding hexadecimal code when pressing keys.

Secondly, the FSM for the real-time clock control unit (CU) to command all the circuit blocks will be studied and finally synthesised into a FPGA or CPLD. A previous work on the design of a multiplexed display will be necessary because the UP2 have only two 7-segments displays available for chip. Again, as in EX2, the proposed design has to be carefully planned (structured) due the large number of blocks involved. Essentially, the project will consist in many VHDL source files to define components to be afterwards instantiated following a hierarchical top-down design approach. The project will be verified using the UP2 Altera board.

1.2 Objectives After completing the task and studying practically all the Chapter 1 units, students will be able to:

- Remember how to design synchronous sequential systems revisiting ED materials- Explain how a FSM can be described as (1) a state register, (2) the next state logic, and (3) the

outputs logic- Search books and the Internet to find information about how a FSM can be coded in VHDL - Describe and conceptualize a digital system as an operational unit (OU) or datapath and a

control unit (CU)- Reinforce the concept of a hierarchical designs using components and their instantiation as the

basis for a good IP (intellectual property) design and documentation- Make projects using Quartus-II software following the design flow which basically consists in:

(1) VHDL source files; (2) functional simulation; (3) pin assignment and synthesis; (4) gate-level simulation; (5) device programming; and (6) prototype verification

- Verify the design (or design components) using the integrated Quartus-II simulator which runs both, functional and gate-level simulation.

- Use RTL, state machine, and technology views as a help to interpret the synthesis process - Use the design summary to get information about the design process and resource usage

(basically registers) - Document the work using a predefined word processor template and utilities: spelling and

grammar, chapter enumeration, page headers and footers, hyperlinks, cross-references, figure captions, text styles, etc.

- Organize the study time and plan the cooperative group work time

1.3 Study time: The estimated student study time for this exercise is 3 weeks4: that means about 20 hours of cooperative work in laboratory sessions (TGA, TGB) or anywhere (TGC).

3 http://epsc.upc.edu/projectes/ed/grups_classe/07-08-q1/1BT4/07-08-Q1-1BT4.htm

3

EPSC – SED: Sistemes Electrònics Digitals

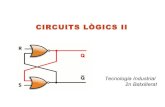

1.4 Designing the 16-key keypad scanning decoder 1.4.1 Keypad characteristics and wiring

A) Find the characteristics of a commercial 16-key keypad like the one represented in Fig. 1. You may run the project downloading the Proteus design from the web page.

1 2 3

654

8 97

0

TS

HS

MS

SSENTER24H/AM-PM

A

B

C

D

1 2 43

Fig. 1 Example of a commercial matrix keypad and the value obtained when pressing key “E” while scanning (setting a “0”) at RowD. Indeed, the DEC2:4 will be an integrated part of the scanning chip, and so, only the 4 pull-up resistors are the necessary hardware for the interface. An adapted keyboard can be easily obtained sticking new plastic labels on the keys (in Proteus-VSM, you can decompose a component, make the required modifications and adding the new component to the library)

1.4.2 Plan the state diagram for the component

B) Invent what is usually called intellectual property (IP): a scanning chip (in our case, a VHDL component) similar to a commercial one like the MM74C922. The chip is based essentially in a FSM running a state diagram for scanning rows and decoding the key pressed.

1.4.3 Synthesize and integrate the component into a new top-level Quartus-II project

C) The scanning chip will work into a new project where all the EX2 blocks are already placed and connected. Remember the design flow, which may be found here5, consisting essentially in:

- (1) VHDL or schematics source files; - (2) functional or behavioural simulation; - (3) device selection, pin assignment (constraints) and project synthesis; - (4) RTL and technology view; - (5) gate-level (timed) simulation; - (6) device programming; and - (7) verification using a prototype board.

The keyboard will be available in the laboratory and ready to be connected to the FLEX_EXPAN_A connector. The pin assignment is as follows:

Row : OUT std_logic_vector(3 downto 0); -- Flex_EXPAN (41, 43, 45, 47) == pins (79, 81, 83, 86)Column : IN std_logic_vector(3 downto 0); -- Flex_EXPAN (49, 51, 53, 55) == pins (88, 95, 98, 100)

-- Flex_EXPAN (57, 59) == VCC

Fig. 2 RTL netlist view for the keyboard decoder identified as a component in the top real time clock system

4 Students will work in cooperative groups for the whole semester. They will work an average time of 6.5 hours per week. 5 http://epsc.upc.edu/projectes/sed/unitats/unitat_1_7/Unitat_1_7.htm

4

EX3: Application project 1: A real-time clock in CPLD or FPGA using VHDL

1.5 Designing the multiplexed 7-segment display system D) Due to the fact that in the UP2 developing board only 2 digits are available for PLD, invent and

code in VHDL a multiplexed display component to be integrated into the general top design, for sending the HH, MM or SS to the FLEX (or MAX) 2-digit displays. For instance, a single key may be used to select which data is send to the displays: HH, if the key is pressed once, MM if pressed twice, and SS if the key is pressed for the third time.

1.6 Designing the real time clock control unit (CU) 1.6.1 State diagram

E) Search Internet (remember that a similar project, designed using classic MSI chips can be run from this reference6) to find ideas and inspiration on how to operate the real time clock from a control unit. Among others, you must plan how to run in normal mode and how to set the time (hours, minutes and seconds) to a desired value acquired from the keyboard. Here you can find some help begin with and to assess the problem complexity: http://epsc.upc.edu/projectes/ed/grups_classe/07-08-q1/1BT4/MI/ED_Curs_07_08_Q1_1BT4_Control_MI-6.docx

CLOCK_COUNTER

CLOCK_SUBSYSTEM

A[3..0] HT[3..0]

TT[3..0]

HT[3..0]

HU[3..0]

TH[3..0]

H[3..0]

MT[3..0]

MU[3..0]

T[3..0]

U[3..0]

ST[3..0]

SU[3..0]

COD[3..0]

HLDTHLDU

MLDT

MLDU

SLDTSLDU

HM

CD

CLK

PM_LEDAM_LED

CEUD_L

HLDTHLDU

MLDT

MLDU

SLDTSLDU

HM

CE

CLK

CD

UD_L

PM_LEDAM_LED

a)

FSM-MOORE

FSM-CONTROL_UNIT

CD

CLK

HLDT

TT

Hours LD tensHLDTHLDU Hours LD unitsHLDU

MLDT Minutes LD tensMLDT

MLDU Minutes LD unitsMLDU

Trigger timer

SLDT Seconds LD tensSLDT

SLDU Seconds LD unitsSLDU

TIMER

TIMER_20_SEG

TTQTQT

Timer out

TS

MSSS

GSD

ENTER

HS

GS

TSHSMSSS

ENTERCE CE

CLOCK_100Hz

CD

b)

Fig. 3 a) Example of a operational unit already produced in EX2 that has to be commanded by a: b) a control unit based on a FSM

1.6.2 Synthesis and implementation

F) Implement the FSM to control the real-time clock

1.7 Improvements and new features G) To the basic clock, you could add new features:

- Chronometer, displaying tenths of seconds- Timer, activating an acoustic or visual signal when time counting down from a

specified value gets 0 - Alarm, activating an acoustic or visual signal when time gets the alarm programmed

value- A serial asynchronous communication port to send data or receive instructions from a

PC. - A battery back-up system, to keep data and the clock running even if power is switched

off. H) Instead of the UP2 training board, you can design your own prototype PCB using software like

EAGLE7 to solder the real-time clock electronic components.

6 http://epsc.upc.edu/projectes/ed/grups_classe/07-08-q1/1BT4/EX/EX7/clock_system_v7B.zip 7 http://epsc.upc.edu/projectes/ed/programari/Programari.html

5

EPSC – SED: Sistemes Electrònics Digitals

Basically, adding characteristics like the ones described above, you can build a system which will have the complexity associated to a final career project. 1.8 Desenvolupament de la pràctica/problema. Treball del grup (títol 2)1.8.1 El vostre primer subtítol (títol 3)

La instal·lació del Quartus-II (títol 4)

Afegiu aquí el vostre text (estil normal) encapçalat amb títols (Títol 2 i 3 i 4), amb figures (estil llegenda o “epígrafe”) i referències creuades en el text com aquesta Fig. 4 (és una referència creuada a la llegenda) a les figures que inseriu. Feu referència també en el text a les fonts bibliogràfiques o de web que consulteu d’aquesta manera [1] (és una referència creuada a l’element numerat [1]). Expliqueu perquè les heu consultat i quina informació útil heu trobat.

Fig. 4 Exemple de peu de figura que segueix la numeració de l’enunciat (llegenda)

1.9 Bibliografia i referències consultadesAmplieu i modifiqueu aquesta secció de referències.

[1] http://epsc.upc.edu/projectes/sed/ . Pàgina web de SED on trobareu materials i treballs de cursos anteriors. Vegeu la secció unitats didàctiques i grups de classe

[2] Brown,S., Vranesic, Z., “Fundamentals of digital logic with VHDL design”, Mc Graw-Hill, 2005

[3] http://epsc.upc.edu/projectes/ed/problemes/problemes_PA/Problemes_PA.htm . Pàgina web d’ED on hi ha el problema que descriu el funcionament i el disseny del descodificador HEX-7SEG.

[4] http://epsc.upc.edu/projectes/sed/projectes_aplicacio/Projectes_Aplic.htm . Lloc on hi trobareu el full de plantilla per a distribuir tasques entre els membres del grup cooperatiu

6

EX3: Application project 1: A real-time clock in CPLD or FPGA using VHDL

1.10 Pla de treball que heu preparat per resoldre el disseny

Consulteu els documents de la web [4] per veure com us podeu preparar el pla de treball i el repartiment de tasques per realitzar una bona feina en equip. Useu diagrames de flux, mapes conceptuals, esquemes, taules, etc.

7

Aquest apartat és obligatori. Si no és present, no es corregeix l’exercici i s’ha de tornar a lliurar

EPSC – SED: Sistemes Electrònics Digitals

1.11 “Fulls de dubtes” de l’EX28

1.11.1 Sobre els apartats A), B) i C) de disseny del codificador del teclat hexadecimal

Grup de treball:

Data:

Pla de treball:

Dubtes:

1.11.2 Sobre l’apartat D) de disseny del multiplexor de displays

Grup de treball:

Data:

Pla de treball:

Dubtes:

8 Afegiu, si és necessari, altres mitjos fulls com aquests per documentar el vostre progrés a través del projecte i poder realitzar consultes i discussions

8

Aquest apartat és obligatori. Si no és present, no es corregeix l’exercici i s’ha de tornar a lliurar

EX3: Application project 1: A real-time clock in CPLD or FPGA using VHDL

1.11.3 Full de dubtes sobre els apartats E) i F) de la unitat de control

Grup de treball:

Data:

Pla de treball:

Dubtes:

9