tarea2_V206

-

Upload

dabasurenpaternina -

Category

Documents

-

view

217 -

download

0

Transcript of tarea2_V206

8/17/2019 tarea2_V206

http://slidepdf.com/reader/full/tarea2v206 1/6

TAREA 2CIRCUITOS LÓGICOS ELECTRÓNICOS

Universidad Tecnológica de Panamá

Facultad de Ingeniería Eléctrica

Circuitos Lógicos Electrónicos

Asignación #2

om!re" a!asuren Paternina

Cedula" $%$$&%'()*

+ru,o"

'EE-(2

Pro.esor"

Elías /endo0a

Fec1a de Entrega"

Lunes ' de Fe!rero de 2&'*

8/17/2019 tarea2_V206

http://slidepdf.com/reader/full/tarea2v206 2/6

TAREA 2CIRCUITOS LÓGICOS ELECTRÓNICOS

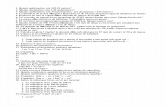

' 3uan 4 /aría Pére0 tienen dos 1i5os6 3osé 4 7usana Cuando salen a comer6 van a un

restorán 8ue sólo sirve 1am!urguesas o a uno 8ue sólo sirven ,ollo Antes de salir6 la

.amilia vota ,ara elegir el restorán +ana la ma4oría6 e9ce,to cuando los ,a,ás están de

acuerdo6 en cu4o caso ellos ganan Cual8uier otro em,ate im,lica ir al restorán de ,ollo

ise:ar un circuito lógico 8ue seleccione en .orma automática el restorán elegido cuando

toda la .amilia vota

8/17/2019 tarea2_V206

http://slidepdf.com/reader/full/tarea2v206 3/6

TAREA 2CIRCUITOS LÓGICOS ELECTRÓNICOS

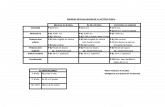

2 etermine el circuito mínimo e8uivalente al 8ue se muestra en la .igura

8/17/2019 tarea2_V206

http://slidepdf.com/reader/full/tarea2v206 4/6

TAREA 2CIRCUITOS LÓGICOS ELECTRÓNICOS

( /inimice la siguiente .unción mediante álge!ra !ooleana

;A6<6C6#6E = >? ;'6)6$6'&6'26'(6'-6')6'@62'62-62*6('=

8/17/2019 tarea2_V206

http://slidepdf.com/reader/full/tarea2v206 5/6

TAREA 2CIRCUITOS LÓGICOS ELECTRÓNICOS

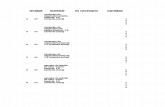

- 7im,li.i8ue las siguientes .unciones mediante un ma,a

a ;A6<6C6#6E = > ? ;'626-6)6*6B6'26'-=

! ;A6<6C6#6E= >

;&6'6)6@6B6''6'26'-=

8/17/2019 tarea2_V206

http://slidepdf.com/reader/full/tarea2v206 6/6

N

O E

S

TAREA 2CIRCUITOS LÓGICOS ELECTRÓNICOS

) La .igura muestra el cruce de una auto,ista ,rinci,al con un camino de acceso

secundario 7e colocan sensores de detección de ve1ículos a lo largo de los carriles C 4

;camino ,rinci,al= 4 en los carriles A 4 < ;camino se acceso= La salidas del sensor son

<A3A ;&= cuando no ,asa ningDn ve1ículo 4 ALTA ;'= cuando ,asa algDn ve1ículo Elsemá.oro del cruce se controlará de acuerdo con la siguiente lógica"

a El semá.oro E% estará en lu0 EGE siem,re 8ue los carriles C 4 estén

ocu,ados

! El semá.oro E% estará la lu0 EGE siem,re 8ue C o estén ocu,ados6 ,ero A

4 < no estén ocu,ados

c El semá.oro %7 estará en lu0 EGE siem,re 8ue los carriles A 4 < estén

ocu,ados6 ,ero C 4 no lo estén

d El semá.oro %7 tam!ién estará en lu0 EGE cuando A o < estén ocu,ados en

tanto 8ue C 4 estén vacíos

e El semá.oro E% estará en lu0 EGE cuando no 1a4a ve1ículos transitando

Utili0ando las salidas del sensor A6 <6 C 4 como entradas6 dise:e un circuito lógico

,ara controlar el semá.oro e!e 1a!er dos salidas H7 4 EH6 8ue ,asen a ALT cuando

la lu0 corres,ondiente se ,one EGE 7im,li.i8ue el circuito lo más 8ue sea ,osi!le